- 您现在的位置:买卖IC网 > PDF目录19389 > ADSP-21266SKSTZ-2D (Analog Devices Inc)IC DSP 32BIT 150MHZ 144-LQFP PDF资料下载

参数资料

| 型号: | ADSP-21266SKSTZ-2D |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 150MHZ 144-LQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,SPI |

| 时钟速率: | 200MHz |

| 非易失内存: | ROM(512 kB) |

| 芯片上RAM: | 256kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

�� �

�

�

�ADSP-21362/ADSP-21363/ADSP-21364/ADSP-21365/ADSP-21366�

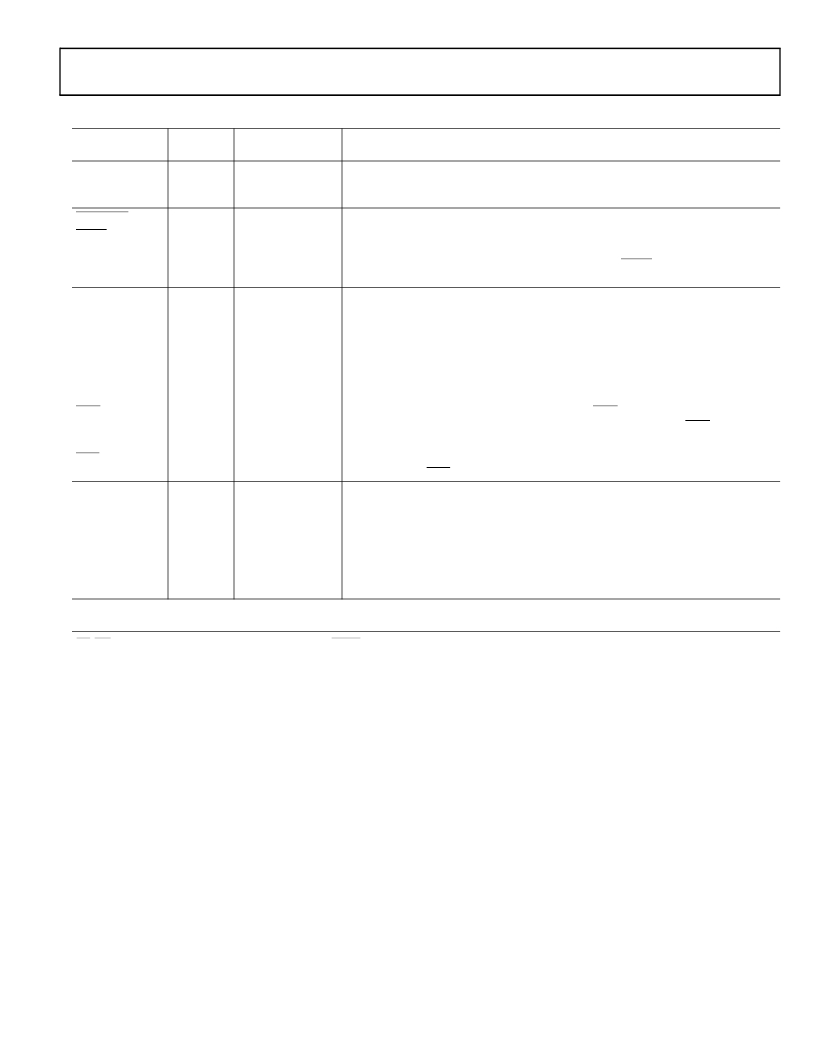

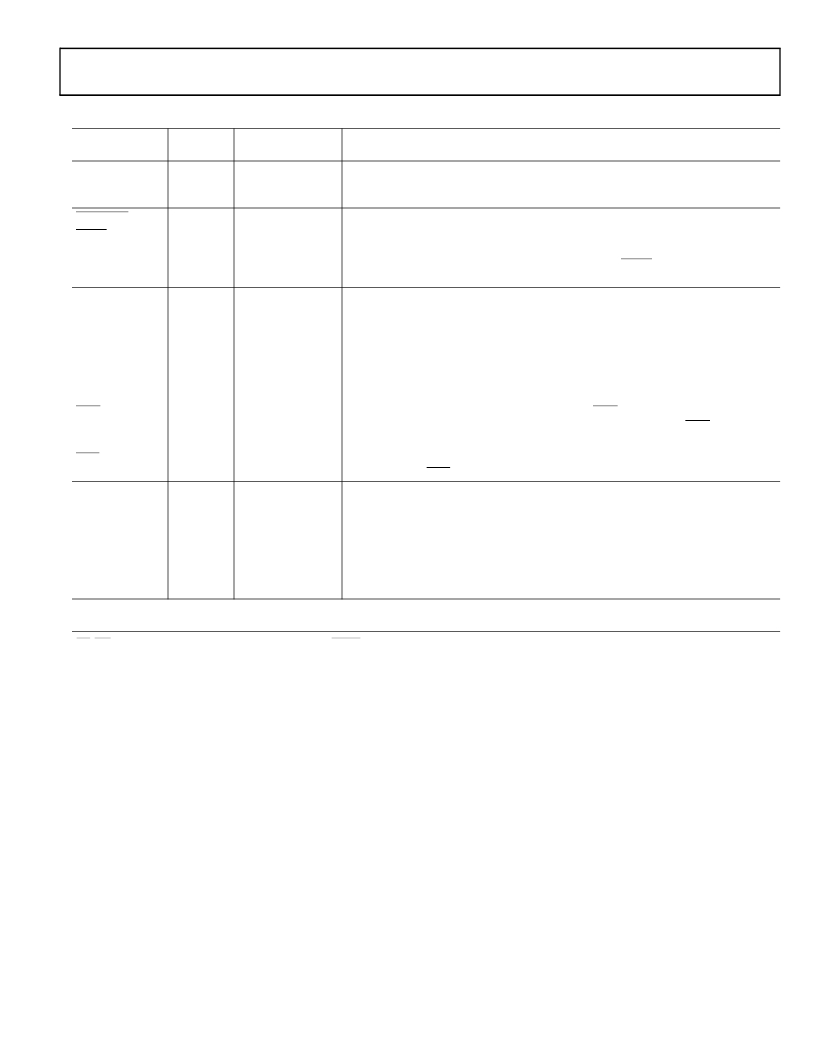

�Table� 6.� Pin� Descriptions� (Continued)�

�State� During� and�

�Pin�

�BOOT_CFG1–0�

�Type�

�I�

�After� Reset�

�Input� only�

�Function�

�Boot� Configuration� Select.� This� pin� is� used� to� select� the� boot� mode� for� the� processor.�

�The� BOOT_CFG� pins� must� be� valid� before� reset� is� asserted.� For� a� description� of� the� boot�

�mode,� refer� to� Table� 5� ,� Boot� Mode� Selection.�

�RESETOUT�

�RESET�

�O� Output� only�

�I/A� Input� only�

�Reset� Out.� Drives� out� the� core� reset� signal� to� an� external� device.�

�Processor� Reset.� Resets� the� ADSP-2136x� to� a� known� state.� Upon� deassertion,� there� is� a�

�4096� CLKIN� cycle� latency� for� the� PLL� to� lock.� After� this� time,� the� core� begins� program�

�execution� from� the� hardware� reset� vector� address.� The� RESET� input� must� be� asserted�

�(low)� at� power-up.�

�TCK� I� Input� only� 3�

�Test� Clock� (JTAG).� Provides� a� clock� for� JTAG� boundary� scan.� TCK� must� be� asserted�

�(pulsed� low)� after� power-up� or� held� low� for� proper� operation� of� the� processors.�

�TMS� I/S�

�(pu)�

�TDI� I/S�

�(pu)�

�Three-state� with�

�pull-up� enabled�

�Three-state� with�

�pull-up� enabled�

�Test� Mode� Select� (JTAG).� Used� to� control� the� test� state� machine.� TMS� has� a� 22.5� k�

�internal� pull-up� resistor.�

�Test� Data� Input� (JTAG).� Provides� serial� data� for� the� boundary� scan� logic.� TDI� has� a�

�22.5� k� internal� pull-up� resistor.�

�TDO� O� Three-state� 4�

�Test� Data� Output� (JTAG).� Serial� scan� output� of� the� boundary� scan� path.�

�TRST�

�I/A�

�(pu)�

�Three-state� with�

�pull-up� enabled�

�Test� Reset� (JTAG).� Resets� the� test� state� machine.� TRST� must� be� asserted� (pulsed� low)�

�after� power-up� or� held� low� for� proper� operation� of� the� ADSP-2136x.� TRST� has� a� 22.5� k�

�internal� pull-up� resistor.�

�EMU�

�V� DDINT�

�V� DDEXT�

�A� VDD�

�O� (O/D)�

�(pu)�

�P�

�P�

�P�

�Three-state� with�

�pull-up� enabled�

�Emulation� Status.� Must� be� connected� to� the� processor� ’s� JTAG� emulators� target� board�

�connector� only.� EMU� has� a� 22.5� k� internal� pull-up� resistor.�

�Core� Power� Supply.� Supplies� the� processor� ’s� core.�

�I/O� Power� Supply.�

�Analog� Power� Supply.� Supplies� the� processor� ’s� internal� PLL� (clock� generator).� This� pin�

�has� the� same� specifications� as� V� DDINT� ,� except� that� added� filtering� circuitry� is� required.� For�

��A� VSS�

�G�

�Analog� Power� Supply� Return.�

�GND� G�

�Power� Supply� Return.�

�The� following� symbols� appear� in� the� Type� column� of� Table� 6� :� A� =� asynchronous,� G� =� ground,� I� =� input,� O� =� output,� P� =� power� supply,�

�S� =� synchronous,� (� A/D� )� =� active� drive,� (� O/D� )� =� open� drain,� and� T� =� three-state,� (� pd� )� =� pull-down� resistor,� (� pu� )� =� pull-up� resistor.�

�1�

�2�

�3�

�4�

�RD,� WR,� and� ALE� are� three-stated� (and� not� driven)� only� when� RESET� is� active.�

�Output� only� is� a� three-state� driver� with� its� output� path� always� enabled.�

�Input� only� is� a� three-state� driver� with� both� output� path� and� pull-up� disabled.�

�Three-state� is� a� three-state� driver� with� pull-up� disabled.�

�Rev.� J� |�

�Page� 13� of� 60� |�

�July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF534BBC-5A | IC DSP CTLR 16BIT 182CSPBGA |

| MAX6643LBBAEE+T | IC CNTRLR FAN SPEED 16-QSOP |

| ADSP-21488KSWZ-3B | IC CCD SIGNAL PROCESSOR 176LQFP |

| ADSP-BF533SBBC500 | IC DSP CTLR 16B 500MHZ 160CSPBGA |

| MAX6644LBAAEE+T | IC CNTRLR FAN SPEED 16-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21267 | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21267SKBCZ-X | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21267SKSTZ-X | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21362 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| adsp-21362bbc-1aa | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。