- 您现在的位置:买卖IC网 > PDF目录19389 > ADSP-21266SKSTZ-2D (Analog Devices Inc)IC DSP 32BIT 150MHZ 144-LQFP PDF资料下载

参数资料

| 型号: | ADSP-21266SKSTZ-2D |

| 厂商: | Analog Devices Inc |

| 文件页数: | 41/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 150MHZ 144-LQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,SPI |

| 时钟速率: | 200MHz |

| 非易失内存: | ROM(512 kB) |

| 芯片上RAM: | 256kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

�� �

�

�

�ADSP-21362/ADSP-21363/ADSP-21364/ADSP-21365/ADSP-21366�

�S/PDIF� Receiver�

�The� following� section� describes� timing� as� it� relates� to� the�

�S/PDIF� receiver.� This� feature� is� not� available� on� the�

�ADSP-21363� processors.�

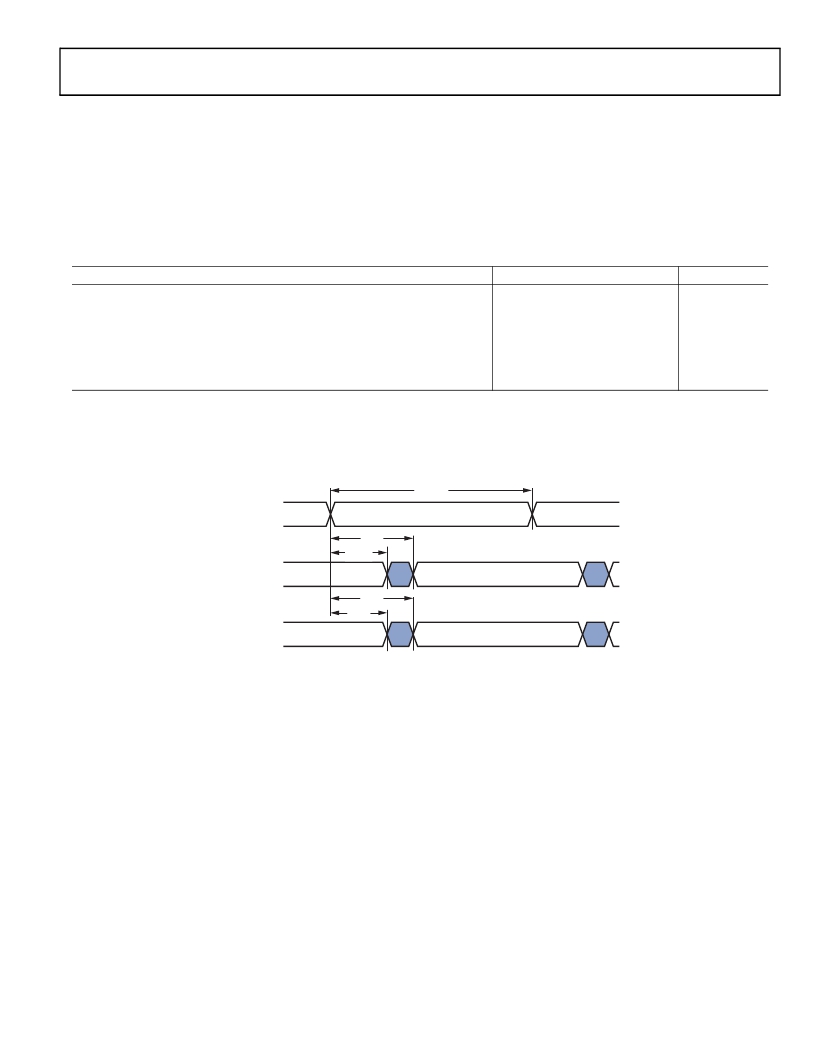

�Internal� Digital� PLL� Mode�

�In� the� internal� digital� phase-locked� loop� mode� the� internal� PLL�

�(digital� PLL)� generates� the� 512� � FS� clock.�

�Table� 38.� S/PDIF� Receiver� Output� Timing� (Internal� Digital� PLL� Mode)�

�Parameter�

�Min�

�Max�

�Unit�

�Switching� Characteristics�

�t� DFSI�

�t� HOFSI�

�t� DDTI�

�t� HDTI�

�t� SCLKIW� 1�

�Frame� Sync� Delay� After� Serial� Clock�

�Frame� Sync� Hold� After� Serial� Clock�

�Transmit� Data� Delay� After� Serial� Clock�

�Transmit� Data� Hold� After� Serial� Clock�

�Transmit� Serial� Clock� Width�

�–2�

�–2�

�38�

�5�

�5�

�ns�

�ns�

�ns�

�ns�

�ns�

�1�

�Serial� clock� frequency� is� 64� ×FS� where� FS� =� the� frequency� of� frame� sync.�

�DRIVE� EDGE�

�SAMPLE� EDGE�

�t� SCLKIW�

�DAI_P20–1�

�(SCLK)�

�t� DFSI�

�t� HOFSI�

�DAI_P20–1�

�(FS)�

�t� DDTI�

�t� HDTI�

�DAI_P20–1�

�(DATA� CHANNEL�

�A/B)�

�Figure� 33.� S/PDIF� Receiver� Internal� Digital� PLL� Mode� Timing�

�Rev.� J� |�

�Page� 41� of� 60� |�

�July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF534BBC-5A | IC DSP CTLR 16BIT 182CSPBGA |

| MAX6643LBBAEE+T | IC CNTRLR FAN SPEED 16-QSOP |

| ADSP-21488KSWZ-3B | IC CCD SIGNAL PROCESSOR 176LQFP |

| ADSP-BF533SBBC500 | IC DSP CTLR 16B 500MHZ 160CSPBGA |

| MAX6644LBAAEE+T | IC CNTRLR FAN SPEED 16-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21267 | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21267SKBCZ-X | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21267SKSTZ-X | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21362 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| adsp-21362bbc-1aa | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。