- 您现在的位置:买卖IC网 > PDF目录19389 > ADSP-21266SKSTZ-2D (Analog Devices Inc)IC DSP 32BIT 150MHZ 144-LQFP PDF资料下载

参数资料

| 型号: | ADSP-21266SKSTZ-2D |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 150MHZ 144-LQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,SPI |

| 时钟速率: | 200MHz |

| 非易失内存: | ROM(512 kB) |

| 芯片上RAM: | 256kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

�� �

�

�

�ADSP-21362/ADSP-21363/ADSP-21364/ADSP-21365/ADSP-21366�

�audio� channels� in� I2S,� left-justified� sample� pair,� or� right-justi-�

�fied� mode.� One� frame� sync� cycle� indicates� one� 64-bit� left/right�

�pair,� but� data� is� sent� to� the� FIFO� as� 32-bit� words� (that� is,� one-�

�half� of� a� frame� at� a� time).� The� processor� supports� 24-� and� 32-bit�

�I� 2� S,� 24-� and� 32-bit� left-justified,� and� 24-,� 20-,� 18-� and� 16-bit�

�right-justified� formats.�

�Precision� Clock� Generator� (PCG)�

�The� precision� clock� generators� (PCG)� consist� of� two� units,� each�

�of� which� generates� a� pair� of� signals� (clock� and� frame� sync)�

�derived� from� a� clock� input� signal.� The� units,� A� and� B,� are� identi-�

�cal� in� functionality� and� operate� independently� of� each� other.�

�The� two� signals� generated� by� each� unit� are� normally� used� as� a�

�serial� bit� clock/frame� sync� pair.�

�SYSTEM� DESIGN�

�The� following� sections� provide� an� introduction� to� system� design�

�options� and� power� supply� issues.�

�Program� Booting�

�The� internal� memory� of� the� processor� boots� at� system� power-up�

�from� an� 8-bit� EPROM� via� the� parallel� port,� an� SPI� master,� an�

�SPI� slave,� or� an� internal� boot.� Booting� is� determined� by� the� boot�

�configuration� (BOOT_CFG1–0)� pins� in� Table� 5� .� Selection� of� the�

�boot� source� is� controlled� via� the� SPI� as� either� a� master� or� slave�

�device,� or� it� can� immediately� begin� executing� from� ROM.�

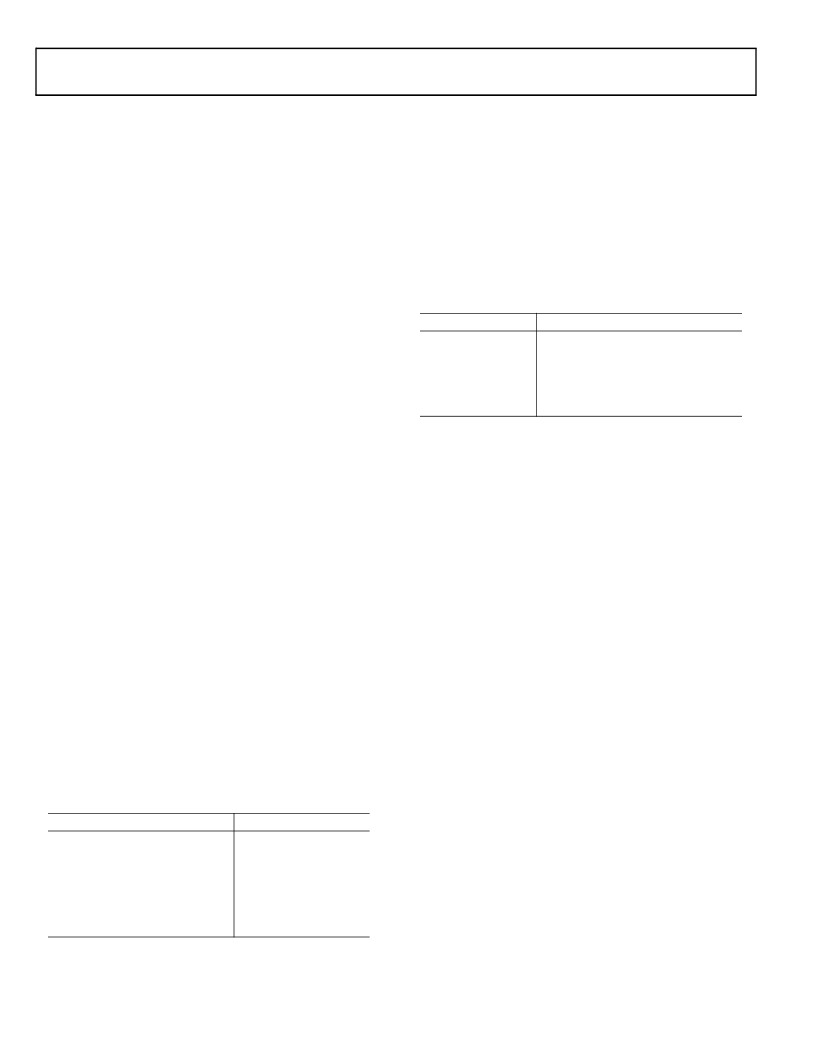

�Table� 5.� Boot� Mode� Selection�

�Peripheral� Timers�

�The� following� three� general-purpose� timers� can� generate� peri-�

�odic� interrupts� and� be� independently� set� to� operate� in� one� of�

�three� modes:�

�?� Pulse� waveform� generation� mode�

�BOOT_CFG1–0�

�00�

�01�

�10�

�11�

�Booting� Mode�

�SPI� Slave� Boot�

�SPI� Master� Boot�

�Parallel� Port� Boot� via� EPROM�

�No� booting� occurs.� Processor� executes�

�?� Pulse� width� count/capture� mode�

�?� External� event� watchdog� mode�

�Each� general-purpose� timer� has� one� bidirectional� pin� and� four�

�registers� that� implement� its� mode� of� operation:� a� 6-bit� configu-�

�ration� register,� a� 32-bit� count� register,� a� 32-bit� period� register,�

�and� a� 32-bit� pulse� width� register.� A� single� control� and� status�

�register� enables� or� disables� all� three� general-purpose� timers�

�independently.�

�I/O� PROCESSOR� FEATURES�

�The� processor’s� I/O� provides� many� channels� of� DMA� and� con-�

�trols� the� extensive� set� of� peripherals� described� in� the� previous�

�sections.�

�DMA� Controller�

�The� processor’s� on-chip� DMA� controllers� allow� data� transfers�

�without� processor� intervention.� The� DMA� controller� operates�

�independently� and� invisibly� to� the� processor� core,� allowing�

�DMA� operations� to� occur� while� the� core� is� simultaneously� exe-�

�cuting� its� program� instructions.� DMA� transfers� can� occur�

�between� the� processor’s� internal� memory� and� its� serial� ports,� the�

�SPI-compatible� (serial� peripheral� interface)� ports,� the� IDP�

�(input� data� port),� the� parallel� data� acquisition� port� (PDAP),� or�

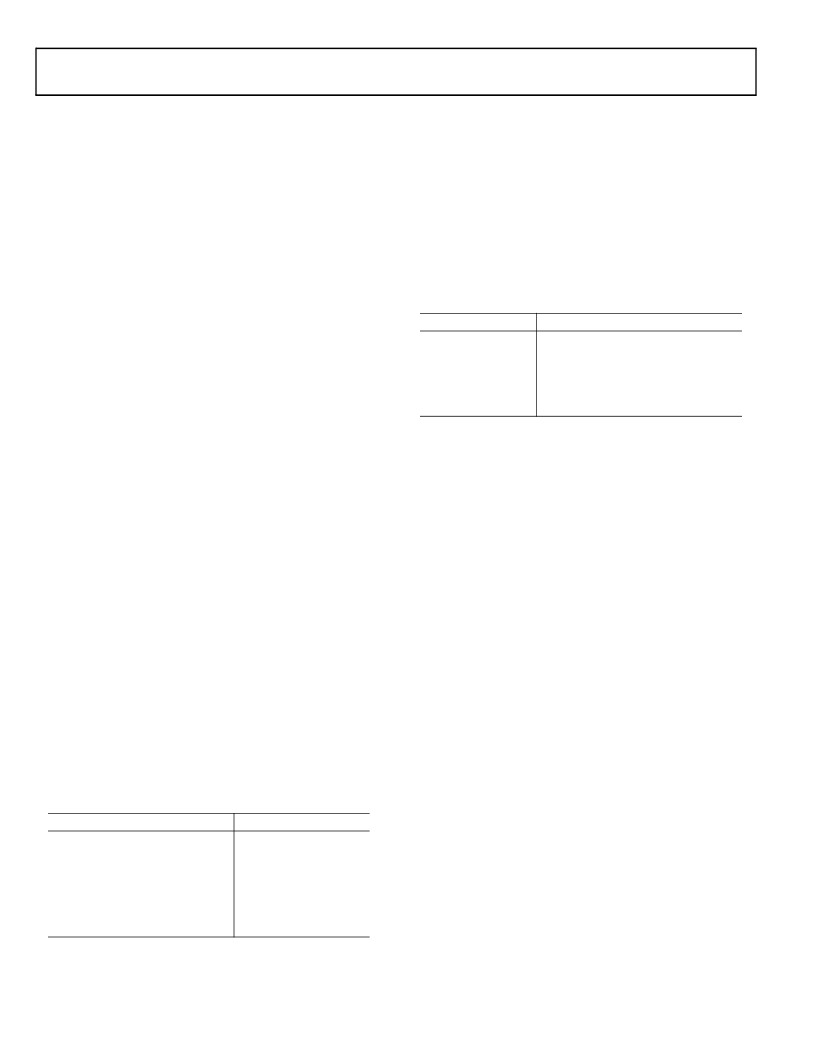

��Table� 4.� DMA� Channels�

�from� internal� ROM� after� reset.�

�Phase-Locked� Loop�

�The� processors� use� an� on-chip� phase-locked� loop� (PLL)� to� gen-�

�erate� the� internal� clock� for� the� core.� On� power-up,� the�

�CLK_CFG1–0� pins� are� used� to� select� ratios� of� 32:1,� 16:1,� and�

�6:1.� After� booting,� numerous� other� ratios� can� be� selected� via�

�software� control.�

�The� ratios� are� made� up� of� software� configurable� numerator� val-�

�ues� from� 1� to� 64� and� software� configurable� divisor� values� of� 1,� 2,�

�4,� and� 8.�

�Power� Supplies�

�The� processor� has� a� separate� power� supply� connection� for� the�

�internal� (V� DDINT� ),� external� (V� DDEXT� ),� and� analog� (A� VDD� /A� VSS� )�

�power� supplies.� The� internal� and� analog� supplies� must� meet� the�

�1.2� V� requirement� for� K,� B,� and� Y� grade� models,� and� the� 1.0� V�

�requirement� for� Y� models.� (For� information� on� the� temperature�

����ment.� All� external� supply� pins� must� be� connected� to� the� same�

�power� supply.�

�Note� that� the� analog� supply� pin� (A� VDD� )� powers� the� processor’s�

�internal� clock� generator� PLL.� To� produce� a� stable� clock,� it� is� rec-�

�ommended� that� PCB� designs� use� an� external� filter� circuit� for� the�

�A� VDD� pin.� Place� the� filter� components� as� close� as� possible� to� the�

�Peripheral�

�SPORTs�

�IDP/PDAP�

�SPI�

�MTM/DTCP�

�Parallel� Port�

�Total� DMA� Channels�

�ADSP-2136x�

�12�

�8�

�2�

�2�

�1�

�25�

�A� VDD� /A� VSS� pins.� For� an� example� circuit,� see� Figure� 3� .� (A�

�recommended� ferrite� chip� is� the� muRata� BLM18AG102SN1D.)�

�To� reduce� noise� coupling,� the� PCB� should� use� a� parallel� pair� of�

�power� and� ground� planes� for� V� DDINT� and� GND.� Use� wide� traces�

�to� connect� the� bypass� capacitors� to� the� analog� power� (A� VDD� )�

�and� ground� (A� VSS� )� pins.� Note� that� the� A� VDD� and� A� VSS� pins�

�specified� in� Figure� 3� are� inputs� to� the� processor� and� not� the� ana-�

�log� ground� plane� on� the� board—the� A� VSS� pin� should� connect�

�directly� to� digital� ground� (GND)� at� the� chip.�

�Rev.� J� |�

�Page� 8� of� 60� |�

�July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF534BBC-5A | IC DSP CTLR 16BIT 182CSPBGA |

| MAX6643LBBAEE+T | IC CNTRLR FAN SPEED 16-QSOP |

| ADSP-21488KSWZ-3B | IC CCD SIGNAL PROCESSOR 176LQFP |

| ADSP-BF533SBBC500 | IC DSP CTLR 16B 500MHZ 160CSPBGA |

| MAX6644LBAAEE+T | IC CNTRLR FAN SPEED 16-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21267 | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21267SKBCZ-X | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21267SKSTZ-X | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21362 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| adsp-21362bbc-1aa | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。