- 您现在的位置:买卖IC网 > PDF目录19383 > ADSP-21368KBPZ-2A (Analog Devices Inc)IC DSP 32BIT 333MHZ 256-BGA PDF资料下载

参数资料

| 型号: | ADSP-21368KBPZ-2A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/64页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 333MHZ 256-BGA |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI |

| 时钟速率: | 333MHz |

| 非易失内存: | ROM(768 kB) |

| 芯片上RAM: | 256kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA 裸露焊盘 |

| 供应商设备封装: | 256-BGA(27x27) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Rev. F

|

Page 15 of 64

|

October 2013

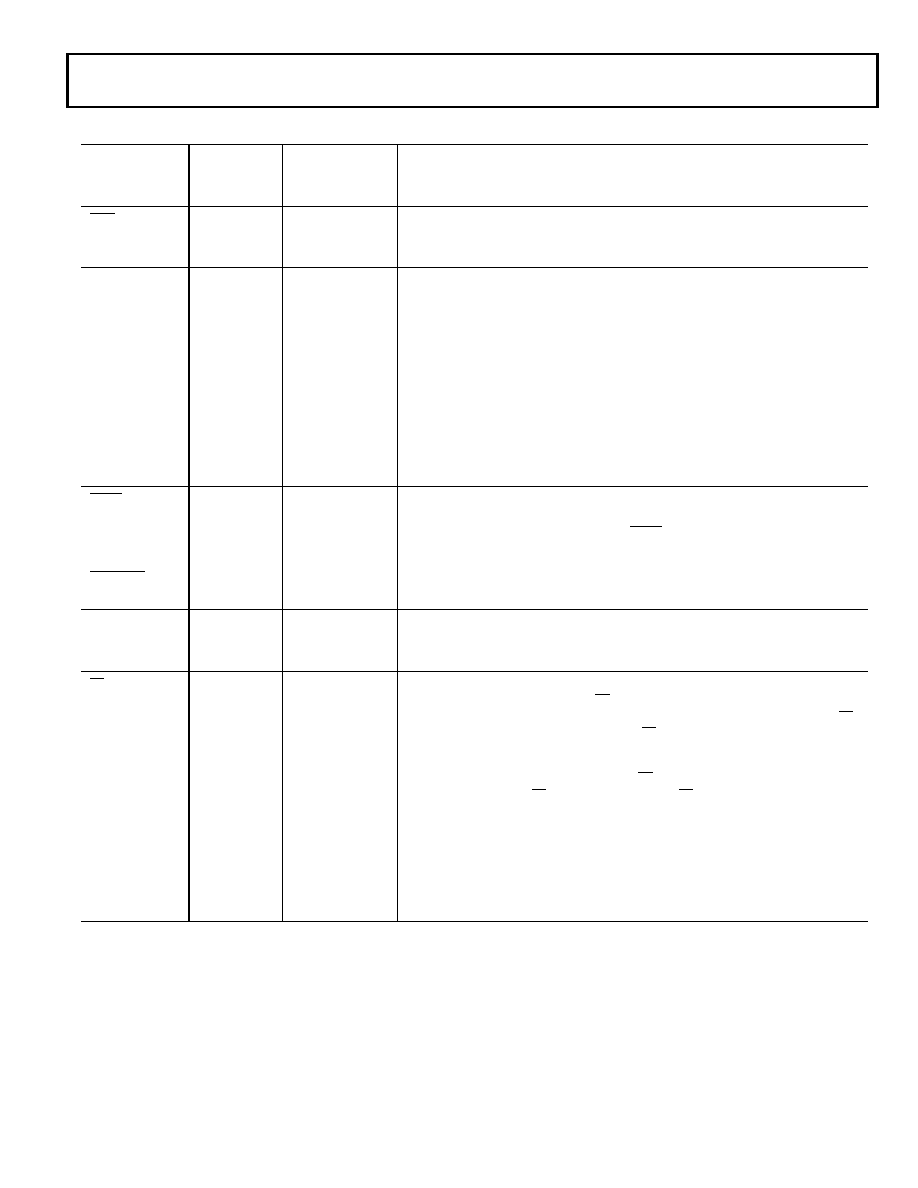

EMU

O (O/D, pu)

Emulation Status. Must be connected to the ADSP-21367/ADSP-21368/

ADSP-21369 Analog Devices DSP Tools product line of JTAG emulator target board con-

nectors only.

CLK_CFG1–0

I

Core/CLKIN Ratio Control. These pins set the start-up clock frequency. See the processor

hardware reference for a description of the clock configuration modes.

Note that the operating frequency can be changed by programming the PLL multiplier

and divider in the PMCTL register at any time after the core comes out of reset.

CLKIN

I

Local Clock In. Used with XTAL. CLKIN is the processor’s clock input. It configures the

processors to use either its internal clock generator or an external clock source. Connect-

ing the necessary components to CLKIN and XTAL enables the internal clock generator.

Connecting the external clock to CLKIN while leaving XTAL unconnected configures the

processor to use an external clock such as an external clock oscillator. CLKIN may not be

halted, changed, or operated below the specified frequency.

XTAL

O

Crystal Oscillator Terminal. Used in conjunction with CLKIN to drive an external crystal.

RESET

I

Processor Reset. Resets the processor to a known state. Upon deassertion, there is a 4096

CLKIN cycle latency for the PLL to lock. After this time, the core begins program execution

from the hardware reset vector address. The RESET input must be asserted (low) at power-

up.

RESETOUT

ODriven low/

driven high

Reset Out. Drives out the core reset signal to an external device.

BOOT_CFG1–0

I

Boot Configuration Select. These pins select the boot mode for the processor. The

BOOT_CFG pins must be valid before reset is asserted. See the processor hardware

reference for a description of the boot modes.

BR4–1

I/O (pu)1

Pulled high/

pulled high

External Bus Request. Used by the ADSP-21368 processor to arbitrate for bus master-

ship. A processor only drives its own BRx line (corresponding to the value of its ID2-0

inputs) and monitors all others. In a system with less than four processors, the unused BRx

pins should be tied high; the processor’s own BRx line must not be tied high or low

because it is an output.

ID2–0

I (pd)

Processor ID. Determines which bus request (BR4–1) is used bythe ADSP-21368 processor.

ID = 001 corresponds to BR1, ID = 010 corresponds to BR2, and so on. Use ID = 000 or 001

in single-processor systems. These lines are a system configuration selection that should

be hardwired or only changed at reset. ID = 101,110, and 111 are reserved.

RPBA

I (pu)1

Rotating Priority Bus Arbitration Select. When RPBA is high, rotating priority for the

ADSP-21368 external bus arbitration is selected. When RPBA is low, fixed priority is

selected. This signal is a system configuration selection which must be set to the same

value on every processor in the system.

1 The pull-up is always enabled on the ADSP-21367 and ADSP-21369 processors. The pull-up on the ADSP-21368 processor is only enabled on the processor with ID2–0 = 00x

2 Pull-up can be enabled/disabled, value of pull-up cannot be programmed.

Table 8. Pin Descriptions (Continued)

Name

Type

State During/

After Reset

(ID = 00x)

Description

相关PDF资料 |

PDF描述 |

|---|---|

| MC79M15CT | IC REG LDO -15V .5A TO220AB |

| TLJR336M004R3000 | CAP TANT 33UF 4V 20% 0805 |

| VI-21T-CW-F4 | CONVERTER MOD DC/DC 6.5V 100W |

| MC79M12CT | IC REG LDO -12V .5A TO220AB |

| VI-2NT-CY-F1 | CONVERTER MOD DC/DC 6.5V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21368KBPZ-3A | 功能描述:IC DSP 32BIT 400MHZ 256BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21368SKBP-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21368SKBPZENG | 制造商:AD 制造商全称:Analog Devices 功能描述:Preliminary Technical Data |

| ADSP-21369 | 制造商:AD 制造商全称:Analog Devices 功能描述:The ADSP-21367/ADSP-21368/ADSP-21369 are available with a 400 MHz core instruction rate with unique audiocentric peripherals such as the digital audio interface, S/PDIF transceiver, serial ports, 8-channel asynchronous sample rate converter, precision clock generators, and more. |

| ADSP-21369BBP-2A | 功能描述:IC DSP 32BIT 333MHZ 256-BGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。