- 您现在的位置:买卖IC网 > PDF目录223311 > ADSP-BF547MBBCZ-5M (ANALOG DEVICES INC) 533 MHz Blackfin Embedded Processor: ADSP-BF547MBBCZ-5M Temp Range: –40°C to +85°C Package: 400-Ball CSP_BGA BC-400-1 PDF资料下载

参数资料

| 型号: | ADSP-BF547MBBCZ-5M |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 533 MHz Blackfin Embedded Processor: ADSP-BF547MBBCZ-5M Temp Range: –40°C to +85°C Package: 400-Ball CSP_BGA BC-400-1 |

| 中文描述: | 16-BIT, 50 MHz, OTHER DSP, PBGA400 |

| 封装: | 17 X 17 MM, ROHS COMPLIANT, CSBGA-400 |

| 文件页数: | 14/100页 |

| 文件大小: | 3095K |

| 代理商: | ADSP-BF547MBBCZ-5M |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

Rev. D

|

Page 20 of 100

|

May 2011

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549

For large page NAND flash devices, the 4-byte electronic

signature is read in order to configure the kernel for boot-

ing. This allows support for multiple large page devices.

The fourth byte of the electronic signature must comply

with the specifications in Table 9.

Any configuration from Table 9 that also complies with the

command set listed below is directly supported by the boot

kernel. There are no restrictions on the page size or block

size as imposed by the small-page boot kernel.

Large page devices must support the following command set:

Large page devices must not support or react to NAND flash

command 0x50. This is a small page NAND flash command

used for device auto detection.

By default, the boot kernel will always issue five address cycles;

therefore, if a large page device requires only four cycles, the

device must be capable of ignoring the additional address cycle.

16-bit NAND flash memory devices must only support the issu-

ing of command and address cycles via the lower eight bits of

the data bus. Devices that use the full 16-bit bus for command

and address cycles are not supported.

Boot from OTP memory (BMODE = 0xB)—This provides

a standalone booting method. The boot stream is loaded

from on-chip OTP memory. By default, the boot stream is

expected to start from OTP page 0x40 and can occupy all

public OTP memory up to page 0xDF (2560 bytes). Since

the start page is programmable, the maximum size of the

boot stream can be extended to 3072 bytes.

Boot from 16-bit host DMA (BMODE = 0xE)—In this

mode, the host DMA port is configured in 16-bit acknowl-

edge mode with little endian data format. Unlike other

modes, the host is responsible for interpreting the boot

stream. It writes data blocks individually into the host

DMA port. Before configuring the DMA settings for each

block, the host may either poll the ALLOW_CONFIG bit in

HOST_STATUS or wait to be interrupted by the HWAIT

signal. When using HWAIT, the host must still check

ALLOW_CONFIG at least once before beginning to con-

figure the host DMA port. After completing the

configuration, the host is required to poll the READY bit in

HOST_STATUS before beginning to transfer data. When

the host sends an HIRQ control command, the boot kernel

issues a CALL instruction to address 0xFFA0 0000. It is the

host’s responsibility to ensure valid code has been placed at

this address. The routine at address 0xFFA0 0000 can be a

simple initialization routine to configure internal

resources, such as the SDRAM controller, which then

returns using an RTS instruction. The routine may also be

the final application, which will never return to the boot

kernel.

Boot from 8-bit host DMA (BMODE = 0xF)—In this

mode, the host DMA port is configured in 8-bit interrupt

mode with little endian data format. Unlike other modes,

the host is responsible for interpreting the boot stream. It

writes data blocks individually to the host DMA port.

Before configuring the DMA settings for each block, the

host may either poll the ALLOW_CONFIG bit in

HOST_STATUS or wait to be interrupted by the HWAIT

signal. When using HWAIT, the host must still check

ALLOW_CONFIG at least once before beginning to con-

figure the host DMA port. The host will receive an

interrupt from the HOST_ACK signal every time it is

allowed to send the next FIFO depth’s worth (sixteen 32-bit

words) of information. When the host sends an HIRQ con-

trol command, the boot kernel issues a CALL instruction to

address 0xFFA0 0000. It is the host's responsibility to

ensure valid code has been placed at this address. The rou-

tine at address 0xFFA0 0000 can be a simple initialization

routine to configure internal resources, such as the

SDRAM controller, which then returns using an RTS

instruction. The routine may also be the final application,

which will never return to the boot kernel.

For each of the boot modes, a 16-byte header is first read from

an external memory device. The header specifies the number of

bytes to be transferred and the memory destination address.

Multiple memory blocks may be loaded by any boot sequence.

Once all blocks are loaded, program execution commences from

the address stored in the EVT1 register.

Prior to booting, the pre-boot routine interrogates the OTP

memory. Individual boot modes can be customized or disabled

based on OTP programming. External hardware, especially

booting hosts, may monitor the HWAIT signal to determine

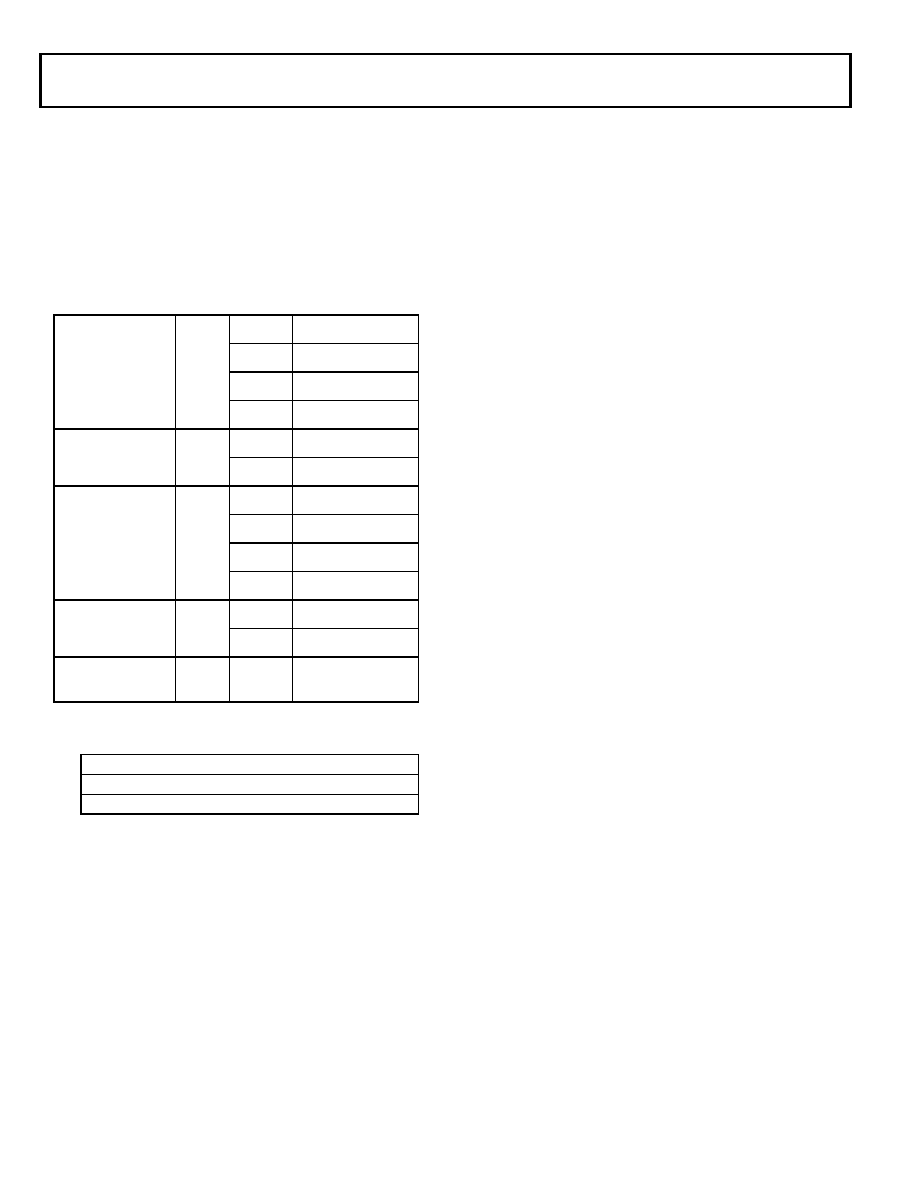

Table 9. Byte 4 Electronic Signature Specification

Page Size (excluding

spare area)

D1:D0

00

1K bytes

01

2K bytes

10

4K bytes

11

8K bytes

Spare Area Size

D2

0

8 bytes/512 bytes

1

16 bytes/512 bytes

Block Size (excluding

spare area)

D5:4

00

64K bytes

01

128K bytes

10

256K bytes

11

512K bytes

Bus Width

D6

0

x8

1x16

Not Used for

Configuration

D3, D7

Reset: 0xFF

Read Electronic Signature: 0x90

Read: 0x00, 0x30 (confirm command)

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF547KBCZ-6A | 600 MHz Blackfin Embedded Processor: ADSP-BF547KBCZ-6A Temp Range: 0°C to +70°C Package: 400-Ball CSP_BGA BC-400-1 |

| ADSP-BF548MBBCZ-5M | 533 MHz Blackfin Embedded Processor: ADSP-BF548MBBCZ-5M Temp Range: –40°C to +85°C Package: 400-Ball CSP_BGA BC-400-1 |

| ADSP-BF548BBCZ-5A | 533 MHz Blackfin Embedded Processor: ADSP-BF548BBCZ-5A Temp Range: –40°C to +85°C Package: 400-Ball CSP_BGA BC-400-1 |

| ADSP-TS101SAB1-000 | 300 MHz TigerSHARC Processor with 6 Mbit on-chip SRAM; Package: 625 ball BGA; No of Pins: 625; Temperature Range: Ind |

| ADSP-TS101SAB2-000 | 300 MHz TigerSHARC Processor with 6 Mbit on-chip SRAM; Package: 484 ball BGA; No of Pins: 484; Temperature Range: Ind |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF547YBC-4A | 功能描述:数字信号处理器和控制器 - DSP, DSC 400MHz Blackfin Embedded Processor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| ADSP-BF547YBCZ-4A | 功能描述:IC DSP BLACKFIN 400MHZ 400CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF548BBCZ | 制造商:Analog Devices 功能描述: |

| ADSP-BF548BBCZ-5A | 功能描述:IC DSP 16BIT 533MHZ 400CSBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF548BBCZ-5AA | 功能描述:IC DSP 16BIT 533MHZ 400CSBGA 制造商:analog devices inc. 系列:Blackfin? 包装:托盘 零件状态:有效 类型:定点 接口:CAN,SPI,SSP,TWI,UART,USB 时钟速率:533MHz 非易失性存储器:外部 片载 RAM:260kB 电压 - I/O:2.50V,3.30V 电压 - 内核:1.25V 工作温度:-40°C ~ 85°C(TA) 安装类型:表面贴装 封装/外壳:400-LFBGA,CSPBGA 供应商器件封装:400-CSPBGA(17x17) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。