- 您现在的位置:买卖IC网 > PDF目录378403 > AN-136 (Integrated Device Technology, Inc.) A NEW GENERATION OF TAG SRAMS?THE IDT71215 AND PDF资料下载

参数资料

| 型号: | AN-136 |

| 厂商: | Integrated Device Technology, Inc. |

| 英文描述: | A NEW GENERATION OF TAG SRAMS?THE IDT71215 AND |

| 中文描述: | 作为TAG SRAM的呢?IDT71215和新一代 |

| 文件页数: | 1/12页 |

| 文件大小: | 103K |

| 代理商: | AN-136 |

Integrated Device Technology, Inc.

1995 Integrated Device Technology, Inc.

1/95

APPLICATION

NOTE

AN-136

A NEW GENERATION OF

TAG SRAMS—THE IDT71215 AND

IDT71216

By Kelly Maas

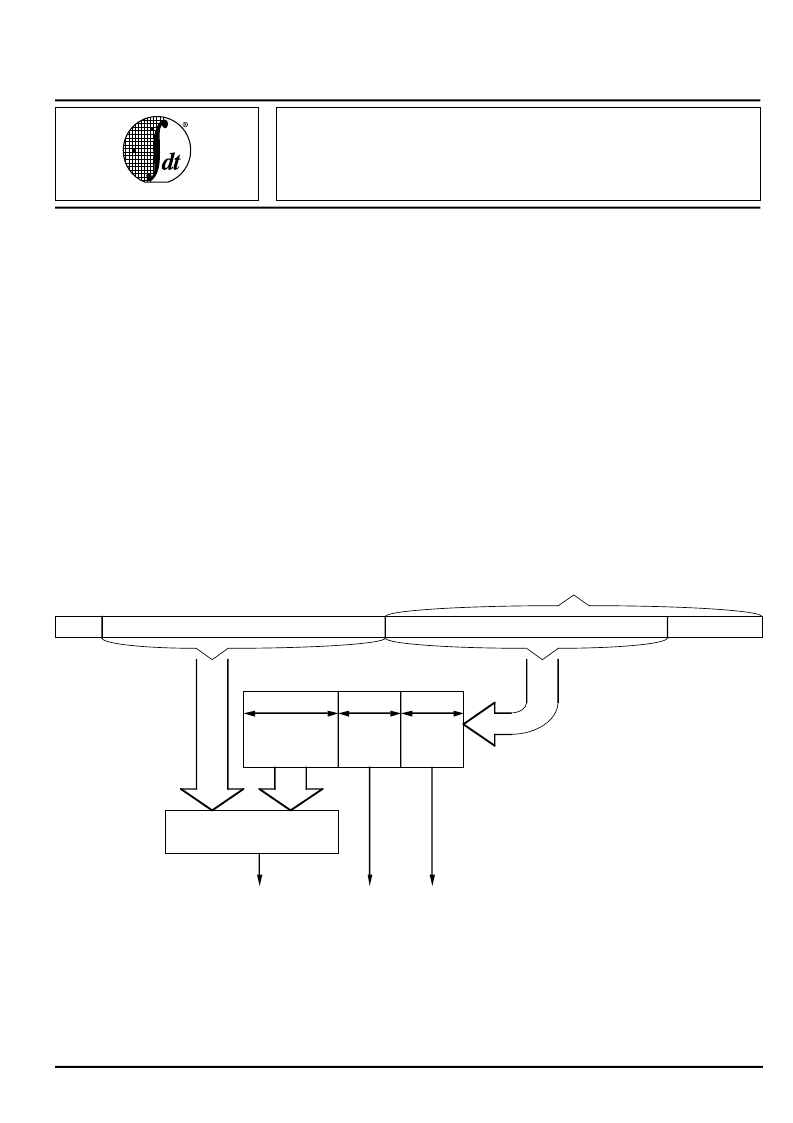

CACHE AND TAG BASICS

For those new to caches, a brief review of cache basics may

be worthwhile. A cache is a memory that provides a CPU with

high speed access to a subset of the data from main memory.

Our discussions are focused on the secondary cache, which

is also known as the L2 cache, but it is not much different from

the faster primary (L1) cache residing inside most CPUs.

The cache consists of a controller, a data memory and a tag

memory. The purpose of the data memory is to store the

active data from main memory, and is composed of either

synchronous burst or asynchronous SRAMs. The tag memory

stores indexes (part of the CPU address field) that indicate

which data is stored in the cache. Additionally, most caches

also require at least one bit of memory for each cache entry,

to indicate the valid or dirty status of that entry. Figure 1 shows

how the CPU address field relates to the cache and the tag

memory. This example includes valid and dirty status bits, and

represents a 512KB cache, 2GB cacheable address space,

32-byte line size, and 8-byte word size.

INTRODUCTION

The 71215 and 71216 represent a new generation of

integrated Tag SRAMs. Just as earlier Tag SRAMs such as

the 71B74 were better suited for tag applications than conven-

tional SRAMs, the 71215/16 go a step further by integrating

new features to significantly ease the design of high perfor-

mance cache subsystems for today’s high speed processors.

These Tag RAMs are designed for easy interfacing to Intel and

PowerPC processors, but are very flexible and can easily be

used in other applications as well.

This application note first provides some background infor-

mation on caches, then describes in detail the architecture

and operation of the 71215 and 71216. This is followed by

three application examples, then a brief discussion of cache

coherency protocol implementation using these Tag RAMs.

Since the 71215 and 71216 are very similar, the descriptions

and explanations in this application note apply to both unless

otherwise noted.

TAG

ADDRESS

A30

A5

TAG

COMPARATOR

A18

A19

TAG MEMORY

LINE

VALID

A4

A3

12

1

1

LINE

DIRTY

MATCH

DATA SRAM ADDRESS

A31

to CACHE CONTROLLER

MSB

LSB

3176 drw 01

Figure 1. CPU Address Field and the L2 Cache (Showing 512 KB cache size and 2 GB cacheable main memory)

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

PowerPC is a trademark of International Business Machines Corporation

Pentium is a trademark of Intel Corporation

相关PDF资料 |

PDF描述 |

|---|---|

| AN-242 | LJT 18C 18#20 SKT RECP |

| AN-40 | Application Note 40 |

| AN-5002 | LJT 18C 18#20 SKT WALL RECP |

| AN-5025 | Applications Using the GTLP10B320 |

| AN-5026 | Circular Connector; No. of Contacts:19; Series:MS27656; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:15; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:15-19 RoHS Compliant: No |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AN137 | 制造商:SILABS 制造商全称:SILABS 功能描述:LITHIUM ION BATTERY CHARGER USING C8051F300 |

| AN1375-521P | 制造商:未知厂家 制造商全称:未知厂家 功能描述:AN0625-521P |

| AN1393 | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Dual Comparators |

| AN1393(AN6914) | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Dual Comparators |

| AN1393S | 制造商:Panasonic Industrial Company 功能描述:IC |

发布紧急采购,3分钟左右您将得到回复。