- 您现在的位置:买卖IC网 > PDF目录379698 > ATT3042-50S132I (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | ATT3042-50S132I |

| 厂商: | Electronic Theatre Controls, Inc. |

| 元件分类: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 现场可编程门阵列 |

| 文件页数: | 35/80页 |

| 文件大小: | 528K |

| 代理商: | ATT3042-50S132I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Data Sheet

February 1997

ATT3000 Series Field-Programmable Gate Arrays

Lucent Technologies Inc.

35

Pin Information

(continued)

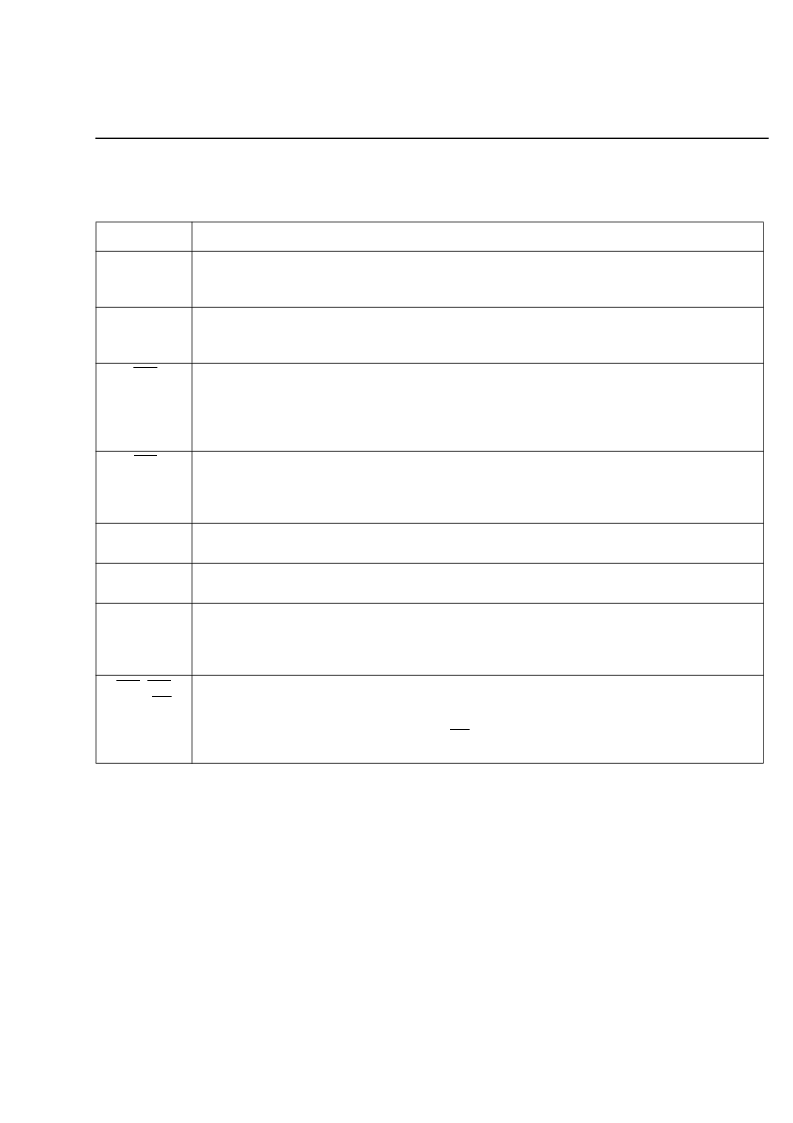

Table 5. I/O Pins with Special Functions

Symbol

Name/Description

M2

Mode 2

. This input has a passive pull-up during configuration. Together with M0 and M1, it is

sampled before the start of configuration to establish the configuration mode to be used. After

configuration, this pin becomes a user-programmable I/O pin.

HDC

High During Configuration

. HDC is held at a high level by the FPGA until after configuration. It

is available as a control output indicating that configuration is not yet completed. After

configuration, this pin is a user I/O pin.

LDC

Low During Configuration

. This active-low signal is held at a low level by the FPGA until after

configuration. It is available as a control output indicating that configuration is not yet completed.

It is particularly useful in master mode as a low enable for an EPROM. After configuration, this

pin is a user I/O pin. If used as a low EPROM enable, it must be programmed as a high after

configuration.

INIT

This is an active-low, open-drain output which is held low during the power stabilization and

internal clearing of the configuration memory. It can be used to indicate status to a configuring

microprocessor or, as a wired-AND of several slave mode devices, a hold-off signal for a master

mode device. After configuration, this pin becomes a user-programmable I/O pin.

BCLKIN

This is a direct CMOS level input to the alternate clock buffer (auxiliary buffer) in the lower right

corner.

XTL1

This user I/O pin can be used to operate as the output of an amplifier driving an external crystal

and bias circuitry.

XTL2

This user I/O pin can be used as the input of an amplifier connected to an external crystal and

bias circuitry. The I/O block is left unconfigured. The oscillator configuration is activated by

routing a net from the oscillator buffer symbol output and by the

ORCA

Foundry bit stream

generation program.

CS0

,

CS1

,

CS2,

WS

These four inputs represent a set of signals, three active-low and one active-high, which are

used in the peripheral mode to control configuration data entry. The assertion of all four

generates a write to the internal data buffer. The removal of any assertion clocks in the D[7:0]

data present. In the master parallel mode,

WS

and CS2 are the A0 and A1 outputs. After

configuration, the pins are user-programmable I/O pins.

相关PDF资料 |

PDF描述 |

|---|---|

| ATT3042-50S44I | Field-Programmable Gate Arrays |

| ATT3042-50S68I | Field-Programmable Gate Arrays |

| ATT3042-50S84I | Field-Programmable Gate Arrays |

| ATT3042-50T132I | Field-Programmable Gate Arrays |

| ATT3042-50T44I | Field-Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATT3042-50S44I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50S68I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50S84I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50T132I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50T44I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。