参数资料

| 型号: | BR93L56RF-WE2 |

| 厂商: | Rohm Semiconductor |

| 文件页数: | 30/41页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 2KBIT 2MHZ 8SOP |

| 标准包装: | 1 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 2K (128 x 16) |

| 速度: | 2MHz |

| 接口: | Microwire 3 线串行 |

| 电源电压: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-SOP |

| 包装: | 标准包装 |

| 产品目录页面: | 1380 (CN2011-ZH PDF) |

| 其它名称: | BR93L56RF-WE2DKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

�� �

�

BR93L� -W� Series,� 93A� □□� -WM� Series,� BR93H� □□� -WC� Series�

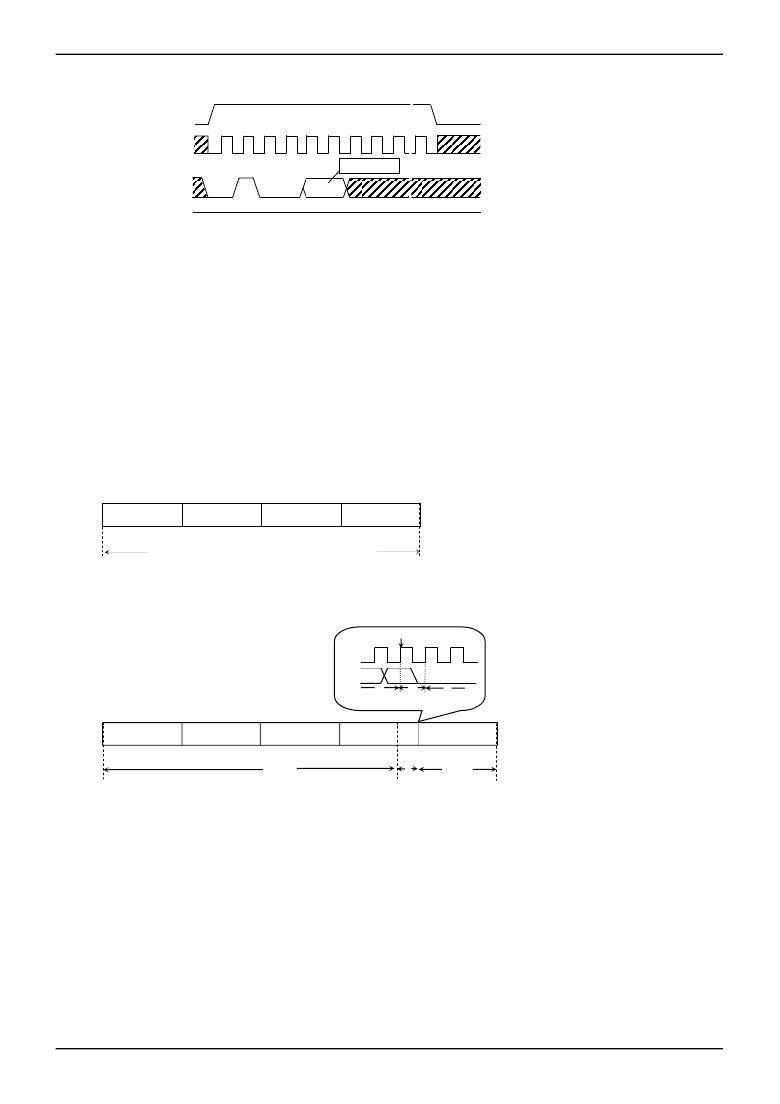

�4)� Write� enable� (WEN)� /� disable� (WDS)� cycle�

�~� ~�

�CS�

�Technical� Note�

�SK�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�~� ~�

�n�

�BR93H56/66-WC� :� n=11�

�ENABLE=1� 1�

�DISABLE=0� 0�

�~� ~�

�BR93H76/86-WC� :� n=13�

�DI�

�1�

�0�

�0�

�~� ~�

�DO�

�High-Z�

�Fig.� 33� Write� enable� (WEN)� /� disable� (WDS)� cycle�

�At� power� on,� this� IC� is� in� write� disable� status� by� the� internal� RESET� circuit.� Before� executing� the� write� command,� it� is�

�necessary� to� execute� the� write� enable� command.� And,� once� this� command� is� executed,� it� is� valid� unitl� the� write� disable�

�command� is� executed� or� the� power� is� turned� off.� However,� the� read� command� is� valid� irrespective� of� write� enable� /�

�disable� command.� Input� to� SK� after� 6� clocks� of� this� command� is� available� by� either� “H”� or� “L”,� but� be� sure� to� input� it.�

�○� When� the� write� enable� command� is� executed� after� power� on,� write� enable� status� gets� in.� When� the� write� disable�

�command� is� executed� then,� the� IC� gets� in� write� disable� status� as� same� as� at� power� on,� and� then� the� write� command� is�

�cancelled� thereafter� in� software� manner.� However,� the� read� command� is� executable.� In� write� enable� status,� even� when�

�the� write� command� is� input� by� mistake,� write� is� started.� To� prevent� such� a� mistake,� it� is� recommended� to� execute� the�

�write� disable� command� after� completion� of� write.�

�●� Application�

�1)� Method� to� cancel� each� command�

�○� READ�

�Start� bit�

�1bit�

�Ope� code�

�2bit�

�Address�

�8bit�

�*1�

�Data�

�16bit�

�*1� Address� is� 8� bits� in� BR93H56-WC,� and� BR93H66-WC.�

�Address� is� 10� bits� in� BR93H76-WC,� and� BR93H86-WC.�

�Cancel� is� available� in� all� areas� in� read� mode.�

�●� Method� to� cancel� :� cancel� by� CS=� “� L� ”�

�Fig.34� READ� cancel� available� timing�

�○� WRITE,� WRAL�

�?� Rise� of� 27clock�

�*2�

�SK�

�DI�

�26�

�D1�

�a�

�27�

�D0�

�b�

�28�

�c�

�29�

�Enlarged� figure�

�Start� bit�

�1bit�

�Ope� code�

�2bit�

�Address�

�8bit�

�*1�

�Data�

�16bit�

�tE/W�

�a�

�b�

�C�

�a� :� From� start� bit� to� 27� clock� rise�

�Cancel� by� CS=“L”�

�b� :� 27� clock� rise� and� after� *� 2�

�Cancellation� is� not� available� by� any� means.� If� Vcc� is� made� OFF� in� this� area,�

�designated� address� data� is� not� guaranteed,� therefore� write� once� again.�

�c� :� 28� clock� rise� and� after� *� 3�

�Cancel� by� CS=“L”�

�However,� when� write� is� started� in� b� area� (CS� is� ended),� cancellation� is� not�

�available� by� any� means.�

�*1� Address� is� 8� bits� in� BR93H56/66-WC�

�Address� is� 10� bits� in� BR93H76/86-WC�

�*2� 27� clocks� in� BR93H56/66-WC�

�29� clocks� in� BR93H76/86-WC�

�*3� 28� clocks� in� BR93H56/66-WC�

�30� clocks� in� BR93H76/86-WC�

�Note� 1)� If� Vcc� is� made� OFF� in� this� area,�

�designated� address� data� is� not� guaranteed,�

�therefore� write� once� again.�

�And� when� SK� clock� is� input� continuously,� cancellation� is� not� available.�

�Note� 2)� If� CS� is� started� at� the� same� timing� as� that� of�

�the� SK� rise,� write� execution/cancel� becomes�

�Fig.35� WRITE,� WRAL� cancel� available� timing�

�unstable,� therefore,� it� is� recommended� to� fail� in�

�SK=”L”� area.� As� for� SK� rise,� recommend� timing� of�

�tCSS/tCSH� or� higher.�

�www.rohm.com�

�?� 2011� ROHM� Co.,� Ltd.� All� rights� reserved.�

�30/40�

�2011.09� -� Rev.G�

�相关PDF资料 |

PDF描述 |

|---|---|

| AGLN125V2-ZCSG81 | IC FPGA NANO 1KB 125K 81-CSP |

| A3PN250-VQ100 | IC FPGA NANO 250K GATES 100-VQFP |

| BR93L46RFJ-WE2 | IC EEPROM 1KBIT 2MHZ 8SOP |

| A3PN250-ZVQG100 | IC FPGA NANO 250K GATES 100-VQFP |

| A3PN250-ZVQ100 | IC FPGA NANO 250K GATES 100-VQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BR93L56-W | 功能描述:IC EEPROM 2KBIT 2MHZ 8DIP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:256K (32K x 8) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:28-TSSOP(0.465",11.8mm 宽) 供应商设备封装:28-TSOP 包装:带卷 (TR) 其它名称:71V256SA15PZGI8 |

| BR93L66 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EEPROM |

| BR93L66F | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EEPROM |

| BR93L66FJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EEPROM |

| BR93L66FJ-W | 制造商:ROHM 制造商全称:Rohm 功能描述:Microwire BUS 4Kbit(256 x 16bit) EEPROM |

发布紧急采购,3分钟左右您将得到回复。