- 您现在的位置:买卖IC网 > PDF目录223464 > BU-66318G0-110 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PQFP208 PDF资料下载

参数资料

| 型号: | BU-66318G0-110 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PQFP208 |

| 封装: | 28 X 28 MM, 1.40 MM HEIGHT, LQFP-208 |

| 文件页数: | 17/32页 |

| 文件大小: | 278K |

| 代理商: | BU-66318G0-110 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

24

Data Device Corporation

www.ddc-web.com

BU-66318

B-09/05-0

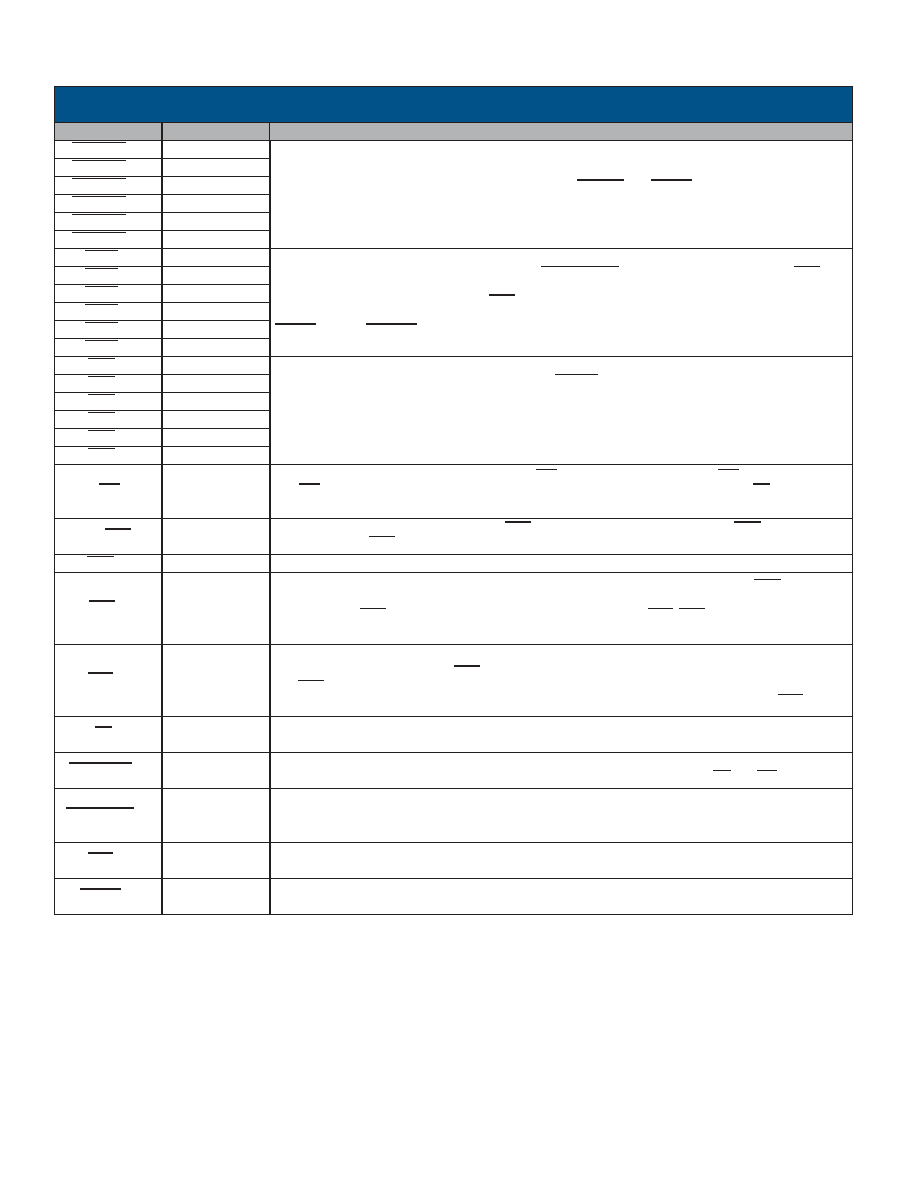

TABLE 26. LOCAL BUS INTERFACE CONTROL

SIGNAL NAME

PIN

DESCRIPTION

SELECT0 (O)

66

SELECT1 (O)

67

SELECT2 (O)

68

SELECT3 (O)

83

SELECT4 (O)

149

SELECT5 (O)

177

RDY0 (I)

69

RDY1 (I)

70

RDY2 (I)

122

RDY3 (I)

97

RDY4 (I)

112

RDY5 (I)

119

INT0 (I)

44

INT1 (I)

61

INT2 (I)

120

INT3 (I)

93

Connected to the respective device [5:0] ACE terminal's SELECT and STRBD signal pins. Address decoder

output to select the ACE for a transfer to/from either RAM or register.

Handshake input from the respective ACE device [5:0] READYD signal pins. For a read access, RDY is

asserted at the end of a host transfer cycle to indicate that data is available to be read on D15 through D0

when asserted (low). For a write cycle, RDY is asserted at the end of the cycle to indicate that data has

been transferred to a register or RAM location. For both reads and writes, the BU-66318 asserts SELECT /

STRBD low until READYD is asserted low.

Interrupt request input from respective ACE devices [5:0]INT signal pins. ACE interrupts are active low sig-

nals.Following a PCI RST#, all connected ACE devices should drive their INT signals inactive high. At this

time the BU-66318 tests its INT [5:0] signals for a low condition. If an active low signal is present, the corre-

sponding ACE device is recorded as "not present".Any unused ACE channel should have its corresponding

INT [5:0] signal grounded.

Read / Write. For ACE or local RAM access, RD/WR selects between reading (RD/WR = 1) and writing

(RD/WR = 0). When the local processor is accessing the ACE-Bridge's internal registers (CS=0) this signal

determines whether an internal register is being written or read.

Memory / Register. For ACE access, MEM/REG selects between ACE memory (MEM/REG = "1") or regis-

ter access (MEM/REG = "0"). When performing a local RAM read, this pin is an output.

Data Transfer Request. Active low level output signal used to request access of the local bus from the local CPU.

Data Transfer Grant. Active low input signal asserted by the local CPU in response to the REQ output to

indicate that control of the local bus has been transferred from the local microprocessor to the ACE-Bridge.

Once asserted, GNT may not be de-asserted prior to the assertion of ACK. GNT must be connected to

ground when a local CPU is not used.

INT4 (I)

96

INT5 (I)

113

RD / WR (I/O)

78

MEM / REG (O)

75

REQ(O)

179

GNT (I)

164

Data Transfer Acknowledge. Active low output signal used to indicate acceptance of the local bus in

response to a data transfer grant GNT. The local bus is always controlled by the BU-66318 during the time

that ACK is asserted low.The BU-66318 will drive all ACE control signals to their in-active (logic '1') state

prior to beginning a transaction and again after completing a transaction, prior to de-asserting ACK.

ACK(O)

178

Chip Select signal input from local CPU indicating that it is accessing BU-66318 internal registers.This sig-

nal must be pulled-up when a local CPU is not used.

CS(I)

175

Chip select signal asserted by BU-66318 when a transfer to local RAM is being performed. When local

RAM is accessed ACE signals RD/WR and MEM/REG will be utilized to generate OE and WE.

LOCAL_CS(O)

9

Interrupt signal to the local processor asserted by the ACE-Bridge in response to any bit being set in REG1

from a PCI write. This signal will remain asserted until the local processor performs a read from the ACE-

Bridge IRQ register.

LOCAL_IRQ(O)

11

Reset signal to the local bus asserted active low following a PCI RST#.

RST(O)

10

Local bus handshake signal to indicate data is valid during a read of the ACE-Bridge's local bus registers

OR that the ACE-Bridge has accepted the data during a write to the ACE-Bridge's internal registers

B_RDY(O)

77

相关PDF资料 |

PDF描述 |

|---|---|

| BU2294AF | 67.735842 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| BU3076HFV-TR | 67.5 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| BU6836 | PCMCIA BUS CONTROLLER, PBGA256 |

| BU7346GUL | 38 MHz, OTHER CLOCK GENERATOR, PBGA6 |

| BUF01900AIDRCR | SPECIALTY ANALOG CIRCUIT, PDSO10 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU6650NUX | 制造商:ROHM 制造商全称:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX_11 | 制造商:ROHM 制造商全称:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX-TR | 功能描述:低压差稳压器 - LDO LDO REG 0.2A 8PIN 2.8V 2.8V 1.8V RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| BU6651NUX | 制造商:ROHM 制造商全称:Rohm 功能描述:High-speed Load Response Full CMOS LDP Regulators |

| BU6651NUX-TR | 功能描述:低压差稳压器 - LDO LDO REG 0.2A 8PIN 2.8V 1.8V 1.5V RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

发布紧急采购,3分钟左右您将得到回复。