- 您现在的位置:买卖IC网 > PDF目录298892 > BX80524P300000 (INTEL CORP) 32-BIT, 300 MHz, MICROPROCESSOR, PPGA370 PDF资料下载

参数资料

| 型号: | BX80524P300000 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 300 MHz, MICROPROCESSOR, PPGA370 |

| 封装: | 1.950 X 1.950 INCH, HEAT SINK, STAGGERED, PLASTIC, PGA-370 |

| 文件页数: | 18/88页 |

| 文件大小: | 1622K |

| 代理商: | BX80524P300000 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

Intel Celeron Processor

Datasheet

25

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all Intel

Celeron processor frequencies.

2. All AC timings for the AGTL+ signals are referenced to the BCLK rising edge at 0.70 V at the processor edge

fingers. This reference is to account for trace length and capacitance on the processor substrate, allowing the

processor core to receive the signal with a reference at 1.25 V. All AGTL+ signal timings (address bus, data

bus, etc.) are referenced at 1.00 V at the processor edge fingers.

3. All AC timings for the CMOS signals are referenced to the BCLK rising edge at 0.70 V at the processor edge

fingers. This reference is to account for trace length and capacitance on the processor substrate, allowing the

processor core to receive the signal with a reference at 1.25 V. All CMOS signal timings (compatibility

signals, etc.) are referenced at 1.25 V at the processor edge fingers.

4. The internal core clock frequency is derived from the Intel Celeron processor system bus clock. The system

bus clock to core clock ratio is determined during initialization. Table 10 shows the supported ratios for each

processor.

5. The BCLK period allows a +0.5 ns tolerance for clock driver variation.

6. This specification applies to Intel Celeron processors when operating at a system bus frequency of 66 MHz.

7. The BCLK offset time is the absolute difference needed between the BCLK signal arriving at the Intel Celeron

processor edge finger at 0.5 V vs. arriving at the core logic at 1.25 V. The positive offset is needed to account

for the delay between the SC242 connector and processor core. The positive offset ensures both the

processor core and the core logic receive the BCLK edge concurrently.

8. See Section 3.1 for Intel Celeron processor system bus clock signal quality specifications.

9. Not 100% tested. Specified by design characterization as a clock driver requirement.

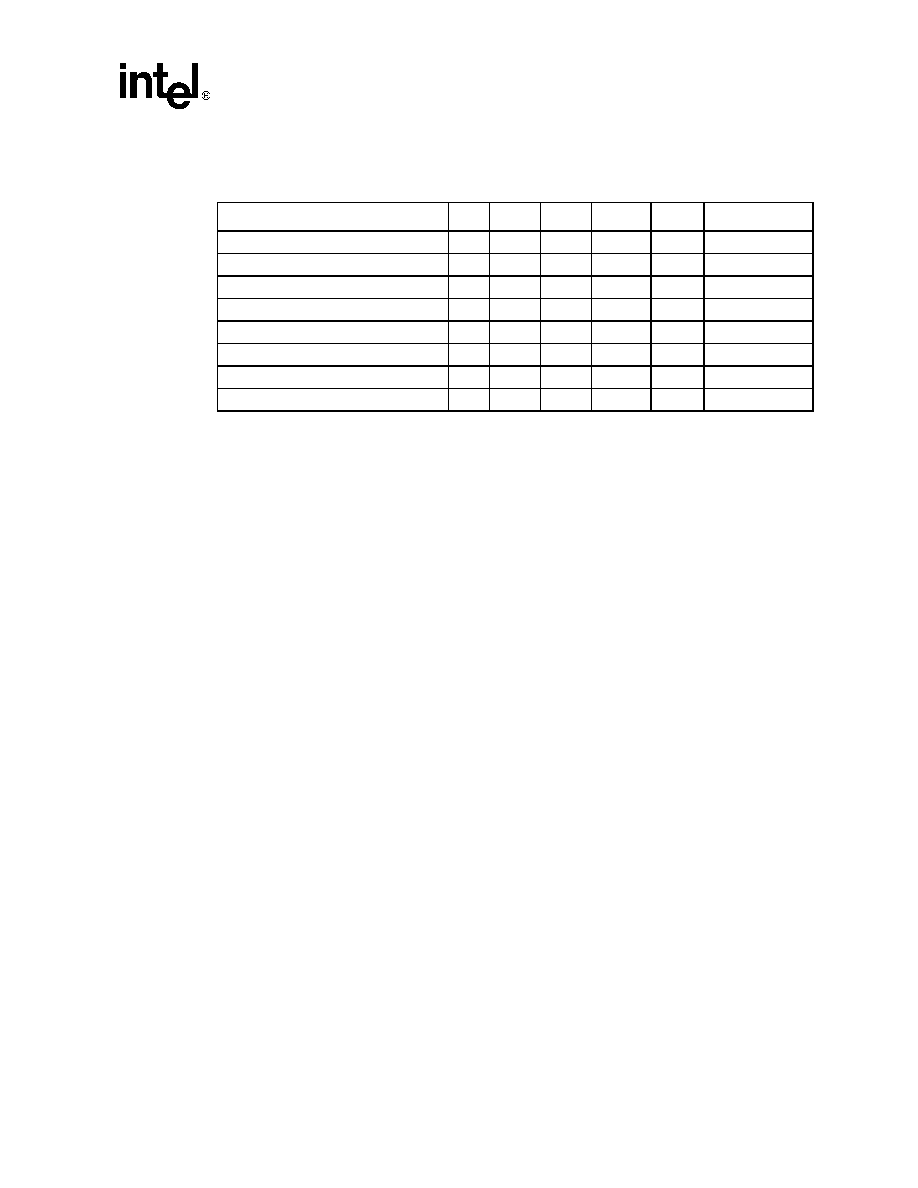

Table 8.

Intel Celeron Processor System Bus AC Specifications (Clock) at the Processor

Edge Fingers For the S.E.P. Package 1, 2, 3

T# Parameter

Min

Nom

Max

Unit

Figure

Notes

System Bus Frequency

66.67

MHz

T1’: BCLK Period

15.0

ns

6

4, 5, 6

T1B’: SC242 to Core Logic BCLK Offset

0.78

ns

6

Absolute Value 7,8

T2’: BCLK Period Stability

± 300ps

See Table 9

T3’: BCLK High Time

4.44

ns

6

@>2.0 V 6

T4’: BCLK Low Time

4.44

ns

6

@<0.5 V 6

T5’: BCLK Rise Time

0.84

2.31

ns

6

(0.5 V–2.0 V) 6, 9

T6’: BCLK Fall Time

0.84

2.31

ns

6

(2.0 V–0.5 V) 6, 9

相关PDF资料 |

PDF描述 |

|---|---|

| BX80525U500512E | 32-BIT, 500 MHz, MICROPROCESSOR, XMA |

| BX80525U533512E | 32-BIT, 533 MHz, MICROPROCESSOR, XMA |

| BX80525U550512E | 32-BIT, 550 MHz, MICROPROCESSOR, XMA |

| BX80525U450512E | 32-BIT, 450 MHz, MICROPROCESSOR, XMA |

| BX80526F500256E | 32-BIT, 500 MHz, MICROPROCESSOR, PPGA370 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BX80524R30012A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:32-Bit Microprocessor |

| BX80524R33312A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:32-Bit Microprocessor |

| BX80525U500256E | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microprocessor |

| BX80525U533256EB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microprocessor |

| BX80525U550256E | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microprocessor |

发布紧急采购,3分钟左右您将得到回复。