- 您现在的位置:买卖IC网 > PDF目录256110 > BX80532RC2300B (INTEL CORP) 32-BIT, 2300 MHz, MICROPROCESSOR PDF资料下载

参数资料

| 型号: | BX80532RC2300B |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 2300 MHz, MICROPROCESSOR |

| 文件页数: | 13/99页 |

| 文件大小: | 4142K |

| 代理商: | BX80532RC2300B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

20

Datasheet

Electrical Specifications

2.7

Asynchronous GTL+ Signals

The Celeron processor on 0.13 micron process does not utilize CMOS voltage levels for any

signals that connect to the processor. As a result, legacy input signals such as A20M#, IGNNE#,

INIT#, LINT0/INTR, LINT1/NMI, SMI#, SLP#, and STPCLK# utilize GTL+ input buffers.

Legacy output FERR# and other non-AGTL+ signals (THERMTRIP# and PROCHOT#) utilize

GTL+ output buffers. All of these signals follow the same DC requirements as AGTL+ signals.

However, the outputs are not actively driven high (during a logical 0 to 1 transition) by the

processor (the major difference between GTL+ and AGTL+). These signals do not have setup or

hold time specifications in relation to BCLK[1:0]. However, all of the Asynchronous GTL+ signals

must be asserted for at least two BCLKs for the processor to recognize them. See Section 2.11 and

Section 2.13 for the DC and AC specifications for the Asynchronous GTL+ signal groups. See

Section 7.2 for additional timing requirements for entering and leaving the low power states.

2.8

Test Access Port (TAP) Connection

Because of the voltage levels supported by other components in the Test Access Port (TAP) logic,

it is recommended that the Celeron processor on 0.13 micron process be first in the TAP chain and

be followed by any other components within the system. A translation buffer should be used to

connect to the rest of the chain unless one of the other components is capable of accepting an input

of the appropriate voltage level. Similar considerations must be made for TCK, TMS, and TRST#.

Two copies of each signal may be required, with each driving a different voltage level.

2.9

System Bus Frequency Select Signals (BSEL[1:0])

The BSEL[1:0] are output signals that are used to select the frequency of the processor input clock

(BCLK[1:0]). Table 5 defines the possible combinations of the signals, and the frequency

associated with each combination. The required frequency is determined by the processor, chipset,

and clock synthesizer. All agents must operate at the same frequency.

The Celeron processor on 0.13 micron process currently operates at a 400 MHz system bus

frequency (selected by a 100 MHz BCLK[1:0] frequency). Individual processors will operate only

at their specified system bus frequency.

For more information about these pins, refer to Section 5.2 and the appropriate Platform Design

Guidelines.

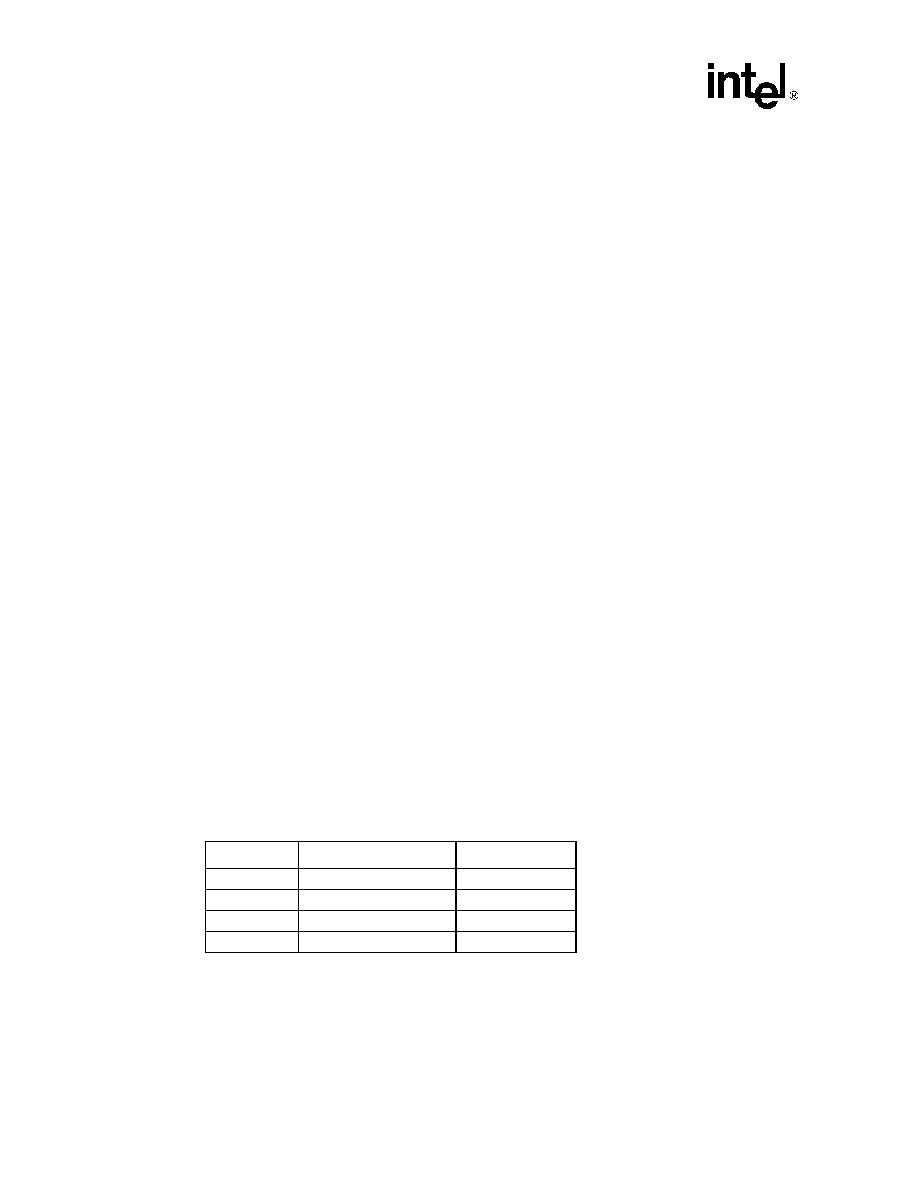

Table 5.

BSEL[1:0] Frequency Table for BCLK[1:0]

BSEL1

BSEL0

Function

L

100 MHz

L

H

RESERVED

H

L

RESERVED

H

RESERVED

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65743F8-310 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-61559D1-390Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-620Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-330Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-330 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BX80532RC2500B | 制造商:Intel 功能描述:MPU CELERON PROCESSOR 0.13UM 2.5GHZ 478-PIN FCPGA2 - Boxed Product (Development Kits) |

| BX80532RC2600B | 制造商:Intel 功能描述:MPU CELERON PROCESSOR 0.13UM 2.6GHZ - Boxed Product (Development Kits) |

| BX80532RC2800B | 制造商:Intel 功能描述:MPU CELERON PROCESSOR 0.13UM 2.8GHZ - Boxed Product (Development Kits) |

| BX80536NC1700EJ | 制造商:Intel 功能描述:MPU CELERON PROCESSOR 390 RISC 64-BIT 90NM 1.7GHZ 1.05V - Boxed Product (Development Kits) |

| BX80537T5500 S L9SH | 制造商:Intel 功能描述:MPU Core?2 Duo Processor T5500 64-Bit 65nm 1.66GHz 1.05V 478-Pin FCPGA6 |

发布紧急采购,3分钟左右您将得到回复。