参数资料

| 型号: | CDB5460AU |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 9/54页 |

| 文件大小: | 0K |

| 描述: | EVALUATION BOARD FOR CS5460A |

| 标准包装: | 1 |

| 主要目的: | 电源管理,电度表/功率表 |

| 嵌入式: | 是,MCU,8 位 |

| 已用 IC / 零件: | CS5460A |

| 主要属性: | 1 相电流和电压监控 |

| 次要属性: | 图形用户接口,SPI? 和 USB 接口 |

| 已供物品: | 板,线缆,软件 |

| 相关产品: | CS5460A-BSZR-ND - IC ENERGY METERING 1PHASE 24SSOP 598-1701-ND - IC PWR/ENERGY 1PH BIDIR 24SSOP 598-1700-ND - IC PWR/ENERGY 1PH BIDIR 24SSOP 598-1094-5-ND - IC ENERGY METERING 1PHASE 24SSOP |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

�� �

�

�

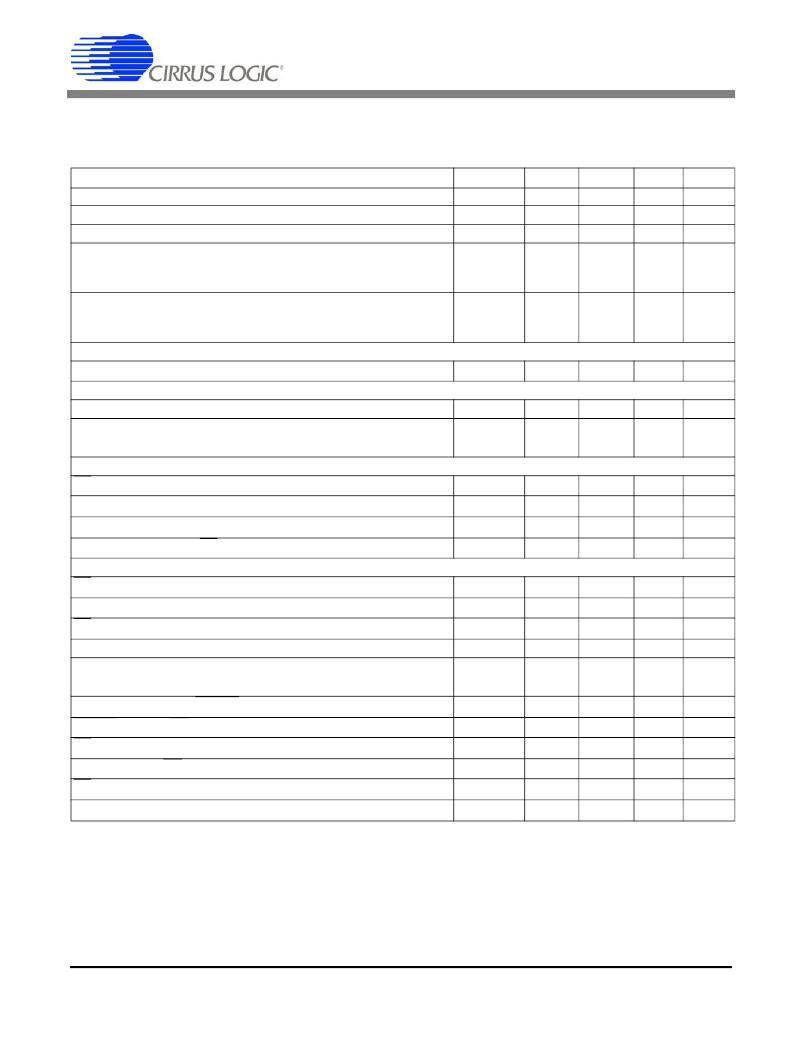

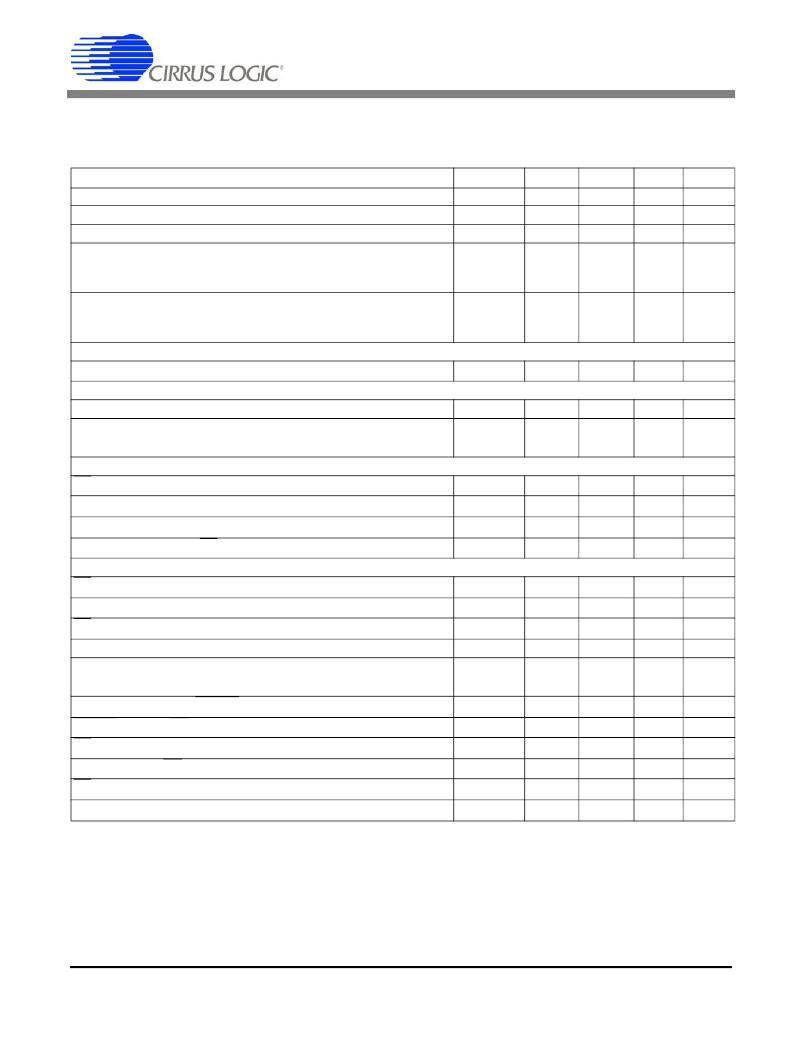

�CS5460A�

�SWITCHING� CHARACTERISTICS�

�(T� A� =� -40� °C� to� +85� °C;� VA+� =� 5.0� V� ±10%;� VD+� =� 3.0� V� ±10%� or� 5.0� V� ±10%;� VA-� =� 0.0� V;� Logic� Levels:�

�Logic� 0� =� 0.0� V,� Logic� 1� =� VD+;� CL� =� 50� pF))�

�Parameter�

�Master� Clock� FrequencyCrystal/Internal� Gate� Oscillator� (Note� 24)�

�Master� Clock� Duty� Cycle�

�CPUCLK� Duty� Cycle� (Note� 25)�

�Rise� Times� Any� Digital� Input� Except� SCLK� (Note� 26)�

�SCLK�

�Any� Digital� Output�

�Fall� Times� Any� Digital� Input� Except� SCLK� (Note� 26)�

�SCLK�

�Any� Digital� Output�

�Symbol�

�MCLK�

�t� rise�

�t� fall�

�Min�

�2.5�

�40�

�40�

�-�

�-�

�-�

�-�

�-�

�-�

�Typ�

�4.096�

�-�

�-�

�-�

�50�

�-�

�-�

�50�

�Max�

�20�

�60�

�60�

�1.0�

�100�

�-�

�1.0�

�100�

�-�

�Unit�

�MHz�

�%�

�%�

�μs�

�μs�

�ns�

�μs�

�μs�

�ns�

�Start-up�

�Oscillator� Start-Up� Time� XTAL� =� 4.096� MHz� (Note� 27)�

�t� ost�

�-�

�60�

�-�

�ms�

�Serial� Port� Timing�

�Serial� Clock� Frequency�

�SCLK�

�-�

�-�

�2�

�MHz�

�Serial� Clock�

�Pulse� Width� High�

�Pulse� Width� Low�

�t� 1�

�t� 2�

�200�

�200�

�-�

�-�

�-�

�-�

�ns�

�ns�

�SD� I� Timing�

�CS� Falling� to� SCLK� Rising�

�Data� Set-up� Time� Prior� to� SCLK� Rising�

�Data� Hold� Time� After� SCLK� Rising�

�SCLK� Falling� Prior� to� CS� Disable�

�t� 3�

�t� 4�

�t� 5�

�t� 6�

�50�

�50�

�100�

�100�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�ns�

�ns�

�ns�

�ns�

�SDO� Timing�

�CS� Falling� to� SDI� Driving�

�SCLK� Falling� to� New� Data� Bit�

�CS� Rising� to� SDO� Hi-Z�

�t� 7�

�t� 8�

�t� 9�

�-�

�-�

�-�

�20�

�20�

�20�

�50�

�50�

�50�

�ns�

�ns�

�ns�

�Auto-boot� Timing�

�Serial� Clock�

�Pulse� Width� High�

�t� 10�

�8�

�MCLK�

�MODE� setup� time� to� RESET� Rising�

�RESET� rising� to� CS� falling�

�Pulse� Width� Low�

�t� 11�

�t� 12�

�t� 13�

�50�

�48�

�8�

�MCLK�

�ns�

�MCLK�

�CS� falling� to� SCLK� rising�

�t� 14�

�100�

�8�

�MCLK�

�SCLK� falling� to� CS� rising�

�CS� rising� to� driving� MODE� low� (to� end� auto-boot� sequence).�

�SDO� guaranteed� setup� time� to� SCLK� rising�

�t� 15�

�t� 16�

�t� 17�

�50�

�100�

�16�

�MCLK�

�ns�

�ns�

�Notes:� 24.� Device� parameters� are� specified� with� a� 4.096� MHz� clock,� yet,� clocks� between� 3� MHz� to� 20� MHz� can� be�

�used.� However,� for� input� frequencies� over� 5� MHz,� an� external� oscillator� must� be� used.�

�25.� If� external� MCLK� is� used,� then� duty� cycle� must� be� between� 45%� and� 55%� to� maintain� this� specification.�

�26.� Specified� using� 10%� and� 90%� points� on� wave-form� of� interest.� Output� loaded� with� 50� pF.�

�27.� Oscillator� start-up� time� varies� with� crystal� parameters.� This� specification� does� not� apply� when� using� an�

�external� clock� source.�

�DS487F5�

�9�

�相关PDF资料 |

PDF描述 |

|---|---|

| CDB5461AU | BOARD EVAL & SOFTWARE CS5461A |

| CDB5466U | BOARD EVAL & SOFTWARE CS5466 ADC |

| CDB5467U | BOARD EVAL FOR CS5467 ADC |

| CDB5560-2 | DEV BOARD FOR CS5560 W/SE INPUT |

| CDB5571-2 | DEV BOARD FOR CS5571 W/SE INPUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDB5460AU-Z | 制造商:Cirrus Logic 功能描述:PB-FREEEVAL BOARD FOR CS5460 - Bulk |

| CDB5461 | 制造商:Cirrus Logic 功能描述:EVAL BD FOR CS5461 - Bulk |

| CDB5461A | 功能描述:EVAL BOARD FOR CS5461 RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 类型:MCU 适用于相关产品:Freescale MC68HC908LJ/LK(80-QFP ZIF 插口) 所含物品:面板、缆线、软件、数据表和用户手册 其它名称:520-1035 |

| CDB5461AU | 功能描述:数据转换 IC 开发工具 Eval Bd Sngl-Phase Pow/Energy RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| CDB5461AU-Z | 制造商:Cirrus Logic 功能描述:PB-FREEEVAL BOARD FOR CS5461 WITH USB - Bulk |

发布紧急采购,3分钟左右您将得到回复。