- 您现在的位置:买卖IC网 > PDF目录170346 > CY39050V208-125NTXI (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 10 ns, PQFP208 PDF资料下载

参数资料

| 型号: | CY39050V208-125NTXI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 10 ns, PQFP208 |

| 封装: | 28 X 28 MM, 0.50 MM PITCH, LEAD FREE, PLASTIC, EQFP-208 |

| 文件页数: | 10/86页 |

| 文件大小: | 2802K |

| 代理商: | CY39050V208-125NTXI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. *I

Page 18 of 86

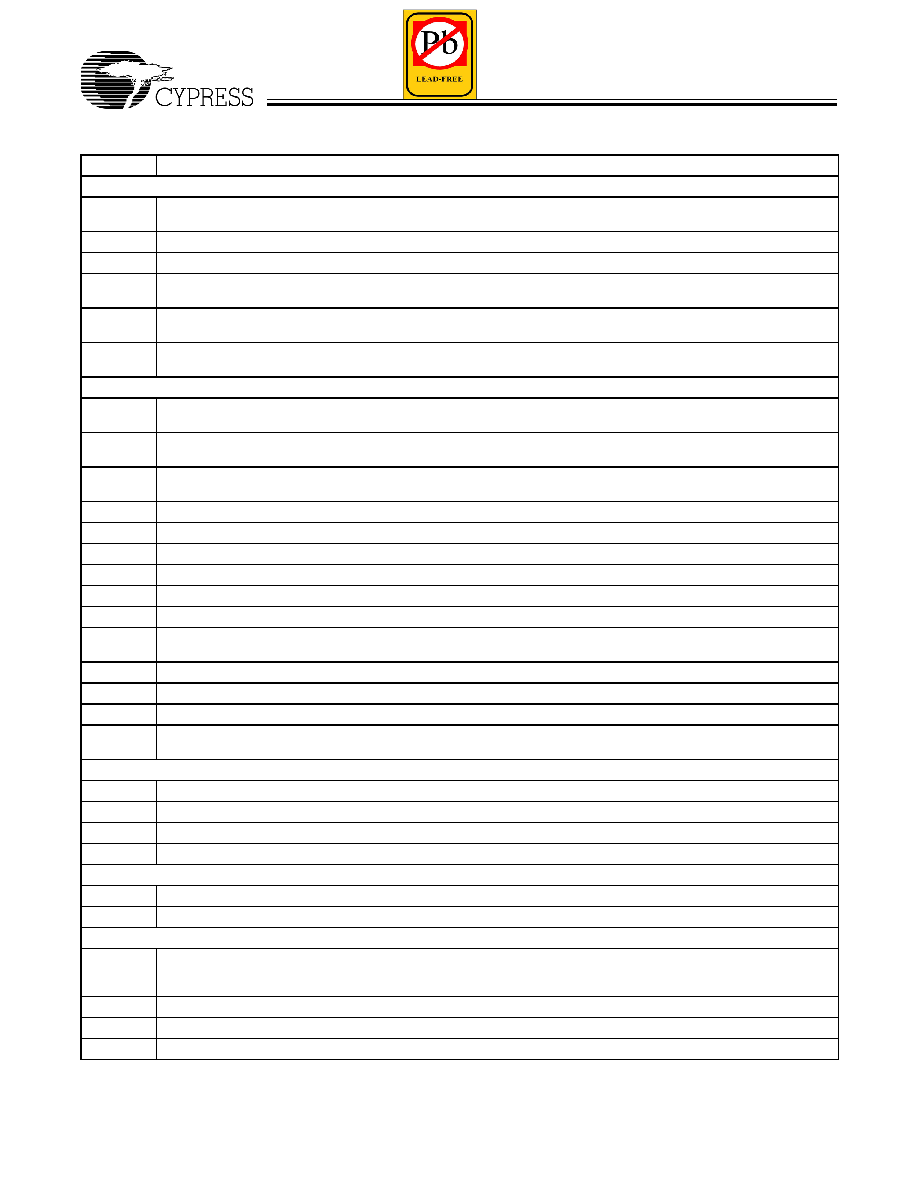

Parameter

Description

Combinatorial Mode Parameters

tPD

Delay from any pin input, through any cluster on the channel associated with that pin input, to any pin output on the

horizontal or vertical channel associated with that cluster

tEA

Global control to output enable

tER

Global control to output disable

tPRR

Asynchronous macrocell RESET or PRESET recovery time from any pin input on the horizontal or vertical channel

associated with the cluster the macrocell is in

tPRO

Asynchronous macrocell RESET or PRESET from any pin input on the horizontal or vertical channel associated

with the cluster that the macrocell is in to any pin output on those same channels

tPRW

Asynchronous macrocell RESET or PRESET minimum pulse width, from any pin input to a macrocell in the farthest

cluster on the horizontal or vertical channel the pin is associated with

Synchronous Clocking Parameters

tMCS

Set-up time of any input pin to a macrocell in any cluster on the channel associated with that input pin, relative to a

global clock

tMCH

Hold time of any input pin to a macrocell in any cluster on the channel associated with that input pin, relative to a

global clock

tMCCO

Global clock to output of any macrocell to any output pin on the horizontal or vertical channel associated with the

cluster that macrocell is in

tIOS

Set-up time of any input pin to the I/O cell register associated with that pin, relative to a global clock

tIOH

Hold time of any input pin to the I/O cell register associated with that pin, relative to a global clock

tIOCO

Clock to output of an I/O cell register to the output pin associated with that register

tSCS

Macrocell clock to macrocell clock through array logic within the same cluster

tSCS2

Macrocell clock to macrocell clock through array logic in different clusters on the same channel

tICS

I/O register clock to any macrocell clock in a cluster on the channel the I/O register is associated with

tOCS

Macrocell clock to any I/O register clock on the horizontal or vertical channel associated with the cluster that the

macrocell is in

tCHZ

Clock to output disable (high-impedance)

tCLZ

Clock to output enable (low-impedance)

fMAX

Maximum frequency with internal feedback—within the same cluster

fMAX2

Maximum frequency with internal feedback—within different clusters at the opposite ends of a horizontal or vertical

channel

Product Term Clock

tMCSPT

Set-up time for macrocell used as input register, from input to product term clock

tMCHPT

Hold time of macrocell used as an input register

tMCCOPT

Product term clock to output delay from input pin

tSCS2PT

Register to register delay through array logic in different clusters on the same channel using a product term clock

Channel Interconnect Parameters

tCHSW

Adder for a signal to switch from a horizontal to vertical channel and vice-versa

tCL2CL

Cluster-to-cluster delay adder (through channels and channel PIM)

Miscellaneous Delays

tCPLD

Delay from the input of a cluster PIM, through a macrocell in the cluster, back to a cluster PIM input. This parameter

can be added to the tPD and tSCS parameters for each extra pass through the AND/OR array required by a given

signal path

tMCCD

Adder for carry chain logic per macrocell

tIOD

Delay from the input of the output buffer to the I/O pin

tIOIN

Delay from the I/O pin to the input of the channel buffer

Note:

13. Add tCHSW to signals making a horizontal to vertical channel switch or vice-versa.

相关PDF资料 |

PDF描述 |

|---|---|

| CY39050V208-233NTXC | LOADABLE PLD, 7.2 ns, PQFP208 |

| CY39050V208-83NTXC | LOADABLE PLD, 15 ns, PQFP208 |

| CY39050V208-83NTXI | LOADABLE PLD, 15 ns, PQFP208 |

| CY39200V208-181NTXC | LOADABLE PLD, 8.5 ns, PQFP208 |

| CY39200V208-83NTXC | LOADABLE PLD, 15 ns, PQFP208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY39050V208-181BBC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181BBI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181BGC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181BGI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181MBC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

发布紧急采购,3分钟左右您将得到回复。