- 您现在的位置:买卖IC网 > PDF目录170346 > CY39050V208-125NTXI (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 10 ns, PQFP208 PDF资料下载

参数资料

| 型号: | CY39050V208-125NTXI |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 10 ns, PQFP208 |

| 封装: | 28 X 28 MM, 0.50 MM PITCH, LEAD FREE, PLASTIC, EQFP-208 |

| 文件页数: | 8/86页 |

| 文件大小: | 2802K |

| 代理商: | CY39050V208-125NTXI |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. *I

Page 16 of 86

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature

(39K200, 208 EQFP) ................................. –45

°C to +125°C

Storage Temperature

(all other densities and packages) .............. –65

°C to +150°C

Soldering Temperature................................................. 220

°C

Ambient Temperature with

Power Applied............................................... –40

°C to +85°C

Junction Temperature...................................................135°C

VCC to Ground Potential...................................–0.5V to 4.6V

VCCIO to Ground Potential................................–0.5V to 4.6V

DC Voltage Applied to Outputs

in High-Z state ..................................................–0.5V to 4.5V

DC Input voltage...............................................–0.5V to 4.5V

DC Current into Outputs........................................ ± 20 mA[6]

Static Discharge Voltage

(per JEDEC EIA./JESD22–A114A)............................ >2001V

Latch-up Current ..................................................... >200 mA

Notes:

6.

DC current into outputs is 36 mA with HSTL III, 48 mA with HSTL IV, and 36 mA with GTL+ (with 25W pull-up resistor and VTT = 1.5).

7.

Input Leakage current is ±10

A for all the pins on all the Delta39K package except the following pins in Delta39K100 packages: The input leakage current spec

for these pins in ±200

A

8.

Not more than one output should be tested at a time. Duration of the short circuit should not exceed 1 second. VOUT = 0.5V has been chosen to avoid test

problems caused by tester-ground degradation. Tested initially and after any design or process changes that may affect these parameters.

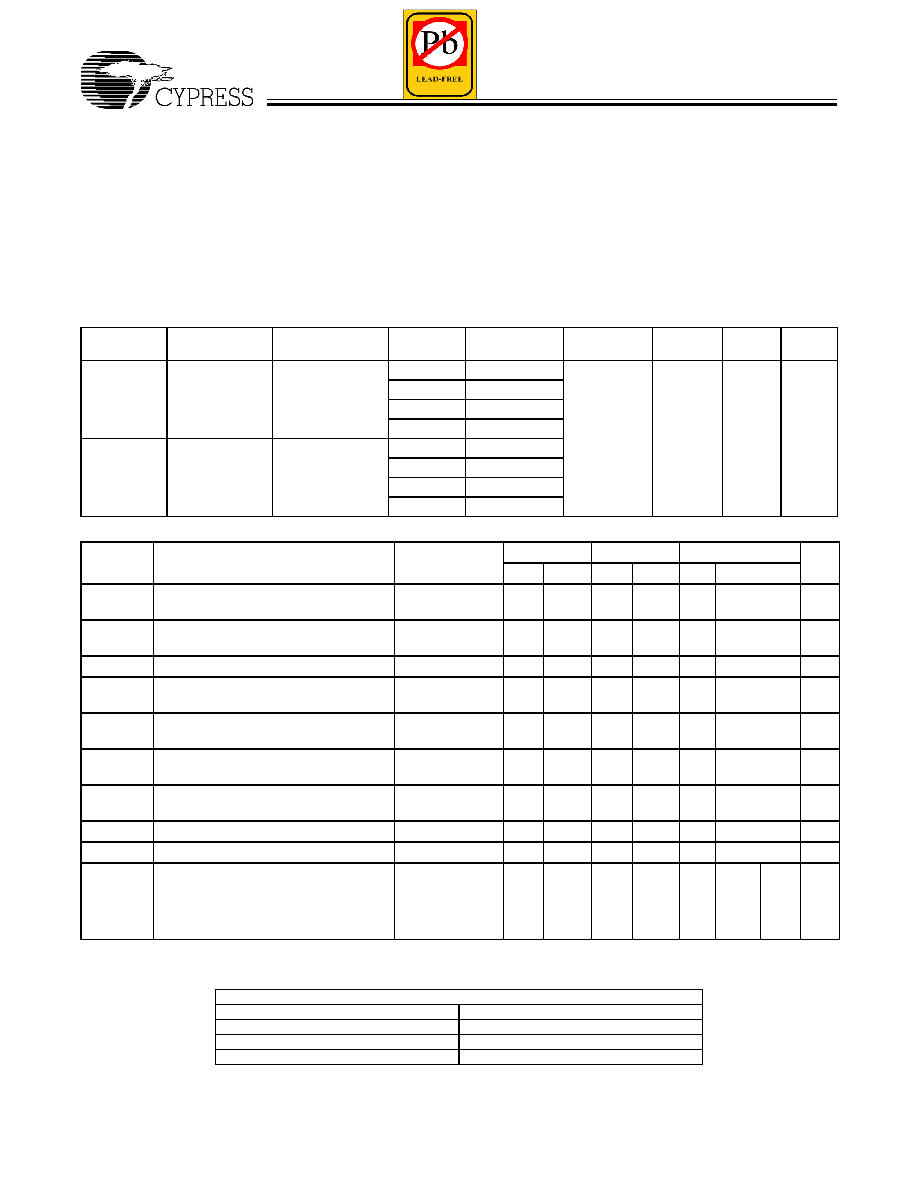

Operating Range

Range

Ambient

Temperature

Junction

Temperature

Output

Condition

VCCIO

VCC

VCCJTAG/

VCCCNFG VCCPLL VCCPRG

Commercial

0

°C to +70°C

0

°C to +85°C

3.3V

3.3V ± 0.3V

3.3V ± 0.3V or

2.5V ± 0.2V

(39KV)

Same as

VCCIO

Sameas

VCC

3.3V ±

0.3V

2.5V

2.5V ± 0.2V

1.8V

1.8V ± 0.15V

1.5V

1.5V ± 0.1V[5]

Industrial

–40

°C to +85°C –40°C to +100°C

3.3V

3.3V ± 0.3V

2.5V

2.5V ± 0.2V

1.8V

1.8V ± 0.15V

1.5V

1.5V ± 0.1V[5]

DC Characteristics

Parameter

Description

Test

Conditions

VCCIO = 3.3V VCCIO = 2.5V

VCCIO = 1.8V

Unit

Min.

Max.

Min.

Max. Min.

Max.

VDRINT

Data Retention VCC Voltage

(config data may be lost below this)

1.5

V

VDRIO

Data Retention VCCIO Voltage

(config data may be lost below this)

1.2

V

IIX[7]

Input Leakage Current

GND

≤ VI ≤ 3.6V

–10

10

–10

10

–10

10

A

IOZ

Output Leakage Current

GND

≤ VO ≤

VCCIO

–10

10

–10

10

–10

10

A

IOS[8]

Output Short Circuit Current

VCCIO = Max.

VOUT = 0.5V

–160

A

IBHL

Input Bus Hold LOW Sustaining Current VCC = Min.

VPIN = VIL

+40

+30

+25

A

IBHH

Input Bus Hold HIGH Sustaining Current VCC = Min.

VPIN = VIH

–40

–30

–25

A

IBHLO

Input Bus Hold LOW Overdrive Current VCC = Max.

+250

+200

+150

A

IBHHO

Input Bus Hold HIGH Overdrive Current VCC = Max.

–250

–200

–150

A

ICC0

Standby Current

39K30

39K50

39K100

39K200

All bins

20

30

60

All bins

20

30

60

–125 bin

3

5

10

–83 bin

12

20

40

A

Delta39K100

Package

Pins

388-BGA

B4, C2

484-FBGA

B8, G9

676-FBGA

F11, J11

相关PDF资料 |

PDF描述 |

|---|---|

| CY39050V208-233NTXC | LOADABLE PLD, 7.2 ns, PQFP208 |

| CY39050V208-83NTXC | LOADABLE PLD, 15 ns, PQFP208 |

| CY39050V208-83NTXI | LOADABLE PLD, 15 ns, PQFP208 |

| CY39200V208-181NTXC | LOADABLE PLD, 8.5 ns, PQFP208 |

| CY39200V208-83NTXC | LOADABLE PLD, 15 ns, PQFP208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY39050V208-181BBC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181BBI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181BGC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181BGI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V208-181MBC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

发布紧急采购,3分钟左右您将得到回复。