- 您现在的位置:买卖IC网 > PDF目录170346 > CY39050V208-222NTC (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 7 ns, PQFP208 PDF资料下载

参数资料

| 型号: | CY39050V208-222NTC |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 7 ns, PQFP208 |

| 封装: | THERMALLY ENHANCED, QFP-208 |

| 文件页数: | 54/57页 |

| 文件大小: | 1166K |

| 代理商: | CY39050V208-222NTC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页当前第54页第55页第56页第57页

PRELIMINARY

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. **

Page 6 of 57

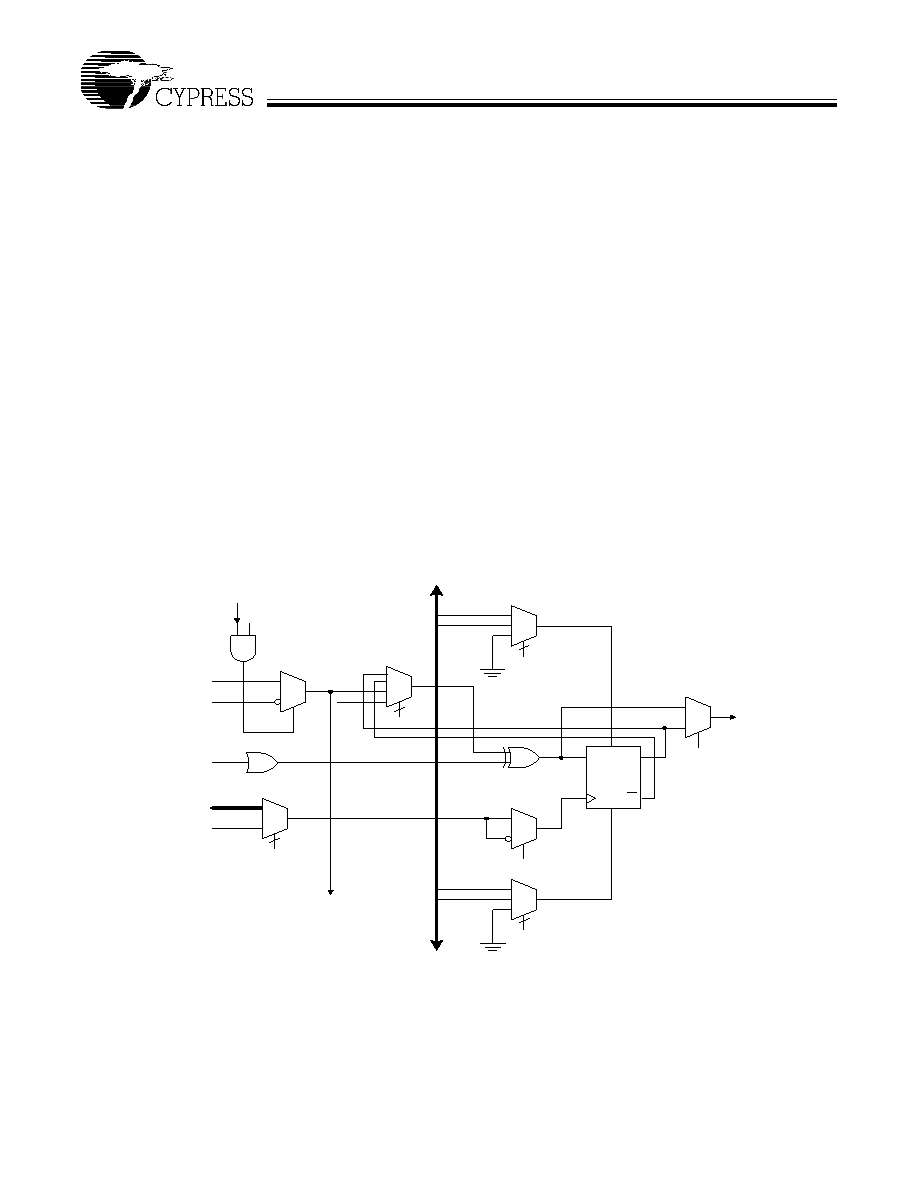

Macrocell

Within each logic block there are 16 macrocells. Each

macrocell accepts a sum of up to 16 product terms from the

product term array. The sum of these 16 product terms can be

output in either registered or combinatorial mode. Figure 4

displays the block diagram of the macrocell. The register can

be asynchronously preset or asynchronously reset at the mac-

rocell level with the separate preset and reset product terms.

Each of these product terms features programmable polarity.

This allows the registers to be preset or reset based on an

AND expression or an OR expression.

An XOR gate in the Delta39K macrocell allows for many differ-

ent types of equations to be realized. It can be used as a po-

larity mux to implement the true or complement form of an

equation in the product term array or as a toggle to turn the D

flip-flop into a T flip-flop. The carry-chain input mux allows ad-

ditional flexibility for the implementation of different types of

logic. The macrocell can utilize the carry chain logic to imple-

ment adders, subtractors, magnitude comparators, parity tree,

or even generic XOR logic. The output of the macrocell is ei-

ther registered or combinatorial.

Carry Chain Logic

The Delta39K macrocell features carry chain logic which is

used for fast and efficient implementation of arithmetic opera-

tions. The carry logic connects macrocells in up to 4 logic

blocks for a total of 64 macrocells. Effective data path opera-

tions are implemented through the use of carry-in arithmetic,

which drives through the circuit quickly. Figure 4 shows that

the carry chain logic within the macrocell consists of two prod-

uct terms (CPT0 and CPT1) from the PTA and an input carry-

in for carry logic. The inputs to the carry chain mux are con-

nected directly to the product terms in the PTA. The output of

the carry chain mux generates the carry-out for the next mac-

rocell in the logic block as well as the local carry input that is

connected to an input of the XOR input mux. Carry-in and a

configuration bit are inputs to an AND gate. This AND gate

provides a method of segmenting the carry chain in any mac-

rocell in the logic block.

Macrocell Clocks

Clocking of the register is highly flexible. Four global synchro-

nous clocks (GCLK[3:0]) and a Product Term clock (PTCLK)

are available at each macrocell register. Furthermore, a clock

polarity mux within each macrocell allows the register to be

clocked on the rising or the falling edge (see macrocell dia-

gram in Figure 4).

PRESET/RESET Configurations

The macrocell register can be asynchronously preset and re-

set using the PRESET and RESET mux. Both signals are ac-

tive high and can be controlled by either of two Preset/Reset

product terms (PRC[1:0] in Figure 4) or GND. In situations

where the PRESET and RESET are active at the same time,

RESET takes priority over PRESET.

Figure 4. Delta39K Macrocell

D

Q

PSET

RES

GCLK[3:0]

PTCLK

FROM PTM

CPT0

CPT1

P

R

C

[1:0]

0

1

0

1

To PIM

C

Carry Out

(to macrocell n+1)

Carry In

(from macrocell n-1)

Up To 16 PTs

PRESET

Mux

Clock

Polarity

Mux

RESET

Mux

Clock Mux

Carry Chain

Mux

XOR Input

Mux

Output Mux

Q

C

3

2

3

C

相关PDF资料 |

PDF描述 |

|---|---|

| CY39050V256-222BBC | LOADABLE PLD, 7 ns, PBGA256 |

| CY39050V388-222MGC | LOADABLE PLD, 7 ns, PBGA388 |

| CY39050V484-222MBC | LOADABLE PLD, 7 ns, PBGA484 |

| CY39050Z208-222NC | LOADABLE PLD, 7 ns, PQFP208 |

| CY39050Z256-222BBC | LOADABLE PLD, 7 ns, PBGA256 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY39050V208-233NTXC | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY39050V208-83NTXC | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY39050V208-83NTXI | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY39050V484-125BBC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V484-125BBI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

发布紧急采购,3分钟左右您将得到回复。