- 您现在的位置:买卖IC网 > PDF目录170346 > CY39050V208-222NTC (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 7 ns, PQFP208 PDF资料下载

参数资料

| 型号: | CY39050V208-222NTC |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 7 ns, PQFP208 |

| 封装: | THERMALLY ENHANCED, QFP-208 |

| 文件页数: | 9/57页 |

| 文件大小: | 1166K |

| 代理商: | CY39050V208-222NTC |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

PRELIMINARY

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. **

Page 17 of 57

Notes:

8.

PCI spec (rev 2.2) requires the IDSEL pin to have capacitance less than or equal to 8 pF. Document titled “Delta39K Pin Tables” identifies all the I/O pins, in a

given package, which can be used as IDSEL in a PCI design. All other I/O pins meet the PCI requirement of capacitance less than or equal to 10 pf.

9.

The number of I/Os which can be used in each I/O bank depends on the type of I/O standards and the number of VCCIO and GND pins being used. Please refer

to the application note titled “Delta39K Family Device I/O Standards and Configurations” for details.

The source current limit per I/O bank per Vccio pin is 165 mA

The sink current limit per I/O bank per GND pin is 230 mA

10. See “Power-up Sequence Requirements” below for VCCIO requirement.

11. 25

resistor terminated to termination voltage of 1.5V.

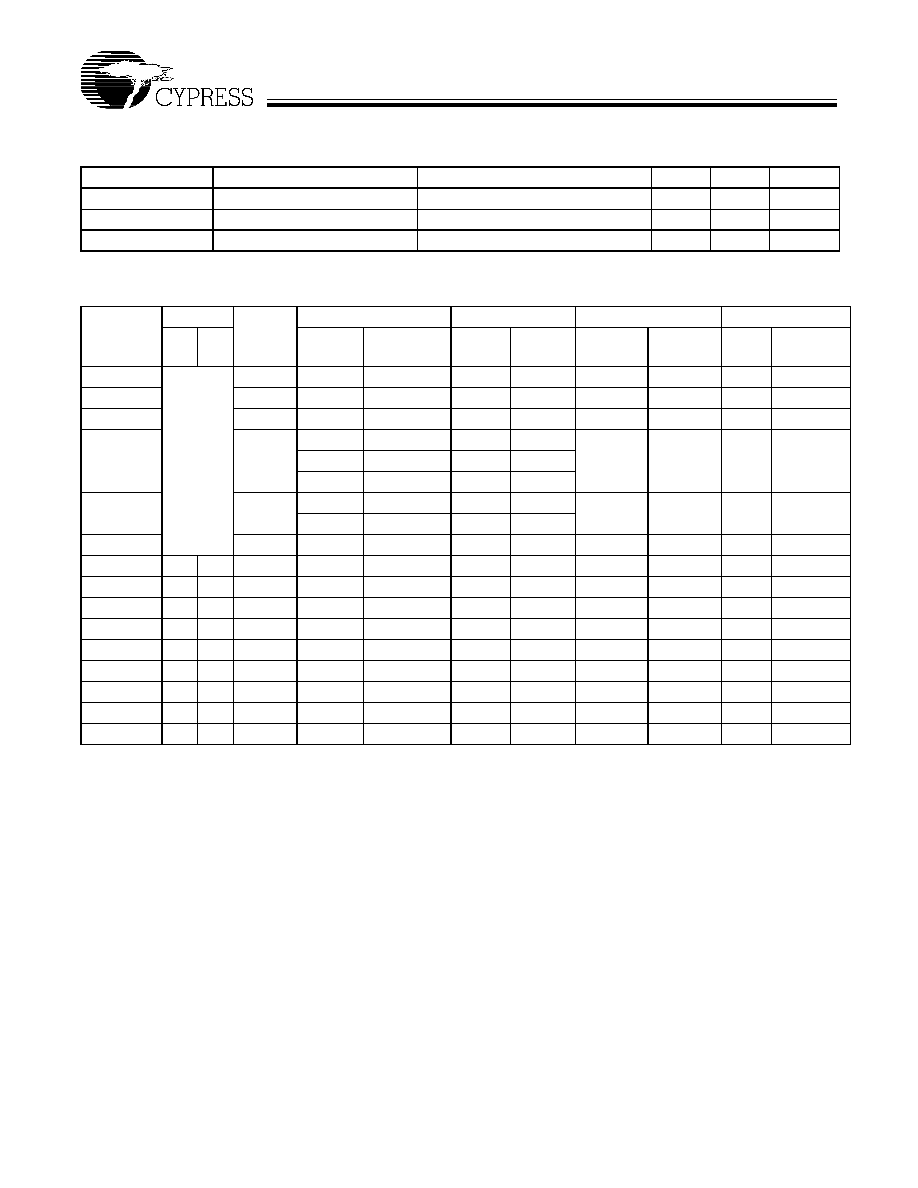

Capacitance

Parameter

Description

Test Conditions

Min.

Max.

Unit

CI/O

Input/Output Capacitance

Vin=VCCIO @ f=1 MHz 25°C

10

pF

CCLK

Clock Signal Capacitance

Vin=VCCIO @ f=1 MHz 25°C

5

12

pF

CPCI

PCI Compliant[8] Capacitance

Vin=VCCIO @ f=1 MHz 25°C

8

pF

DC Characteristics (IO)[9]

Input/

Output

Standard

VREF (V)

VCCIO

(V)

VOH (V)

VOL (V)

VIH (V)

VIL (V)

Mi

n

.

Max

.

@ IOH =VOH (min.)

@ IOL =

VOL

(max.)

Min.

Max.

Min.

Max.

LVTTL

N/A

3.3

–4 mA

2.4

4 mA

0.4

2.0 V

VCCIO+0.3 –0.3V

0.8V

LVCMOS

3.3

–0.1 mA

VCCIO–0.2v

0.1 mA

0.2

2.0 V

VCCIO+0.3 –0.3V

0.8V

LVCMOS3

3.0

–0.1 mA

VCCIO–0.2v

0.1mA

0.2

2.0 V

VCCIO+0.3 –0.3V

0.8V

LVCMOS2

2.5

–0.1 mA

2.1

0.1 mA

0.2

1.7 V

VCCIO+0.3 –0.3V

0.7V

–1.0 mA

2.0

1.0 mA

0.4

–2.0 mA

1.7

2.0 mA

0.7

LVCMOS18

1.8

–0.1 mA

VCCIO–0.2v

0.1mA

0.2

0.65VCCIO VCCIO+0.3 –0.3V

0.35VCCIO

– 2 mA

VCCIO–0.45v 2.0 mA

0.45

3.3V PCI

3.3

–0.5 mA

0.9VCCIO

1.5 mA

0.1VCCIO 0.5VCCIO VCCIO+0.5 –0.5V

0.3VCCIO

GTL+

0.9

1.1

Note 10

Note 11

0.6

VREF+0.2

VREF–0.2

SSTL3 I

1.3

1.7

3.3

–8 mA

VCCIO–1.1v

8 mA

0.7

VREF+0.2 VCCIO+0.3 –0.3V

VREF–0.2

SSTL3 II

1.3

1.7

3.3

–16 mA

VCCIO–0.9v

16 mA

0.5

VREF+0.2 VCCIO+0.3 –0.3V

VREF–0.2

SSTL2 I

1.15 1.35

2.5

–7.6 mA

VCCIO–0.62v 7.6 mA

0.54

VREF+1.8 VCCIO+0.3 –0.3V VREF–0.18

SSTL2 II

1.15 1.35

2.5

–15.2 mA VCCIO–0.43v 15.2 mA

0.35

VREF+1.8 VCCIO+0.3 –0.3V VREF–0.18

HSTL I

0.68

0.9

1.5

–8 mA

VCCIO–0.4v

8 mA

0.4

VREF+1.0 VCCIO+0.3 –0.3V

VREF–0.1

HSTL II

0.68

0.9

1.5

–16 mA

VCCIO–0.4v

16 mA

0.4

VREF+1.0 VCCIO+0.3 –0.3V

VREF–0.1

HSTL III

0.68

0.9

1.5

–8 mA

VCCIO–0.4v

24 mA

0.4

VREF+1.0 VCCIO+0.3 –0.3V

VREF–0.1

HSTL IV

0.68

0.9

1.5

–8 mA

VCCIO–0.4v

48 mA

0.4

VREF+1.0 VCCIO+0.3 –0.3V

VREF–0.1

相关PDF资料 |

PDF描述 |

|---|---|

| CY39050V256-222BBC | LOADABLE PLD, 7 ns, PBGA256 |

| CY39050V388-222MGC | LOADABLE PLD, 7 ns, PBGA388 |

| CY39050V484-222MBC | LOADABLE PLD, 7 ns, PBGA484 |

| CY39050Z208-222NC | LOADABLE PLD, 7 ns, PQFP208 |

| CY39050Z256-222BBC | LOADABLE PLD, 7 ns, PBGA256 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY39050V208-233NTXC | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY39050V208-83NTXC | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY39050V208-83NTXI | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:Delta 39K™ ISR™ 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| CY39050V484-125BBC | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V484-125BBI | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

发布紧急采购,3分钟左右您将得到回复。