- 您现在的位置:买卖IC网 > PDF目录295374 > CY7C1177V18-333BZXC (CYPRESS SEMICONDUCTOR CORP) 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.5 Cycle Read Latency) PDF资料下载

参数资料

| 型号: | CY7C1177V18-333BZXC |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | SRAM |

| 英文描述: | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.5 Cycle Read Latency) |

| 中文描述: | 2M X 9 DDR SRAM, 0.45 ns, PBGA165 |

| 封装: | 13 X 15 MM, 1.40 MM HEIGHT, LEAD FREE, MO-216, FBGA-165 |

| 文件页数: | 25/27页 |

| 文件大小: | 648K |

| 代理商: | CY7C1177V18-333BZXC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页

CY7C1166V18, CY7C1177V18

CY7C1168V18, CY7C1170V18

Document Number: 001-06620 Rev. *D

Page 7 of 27

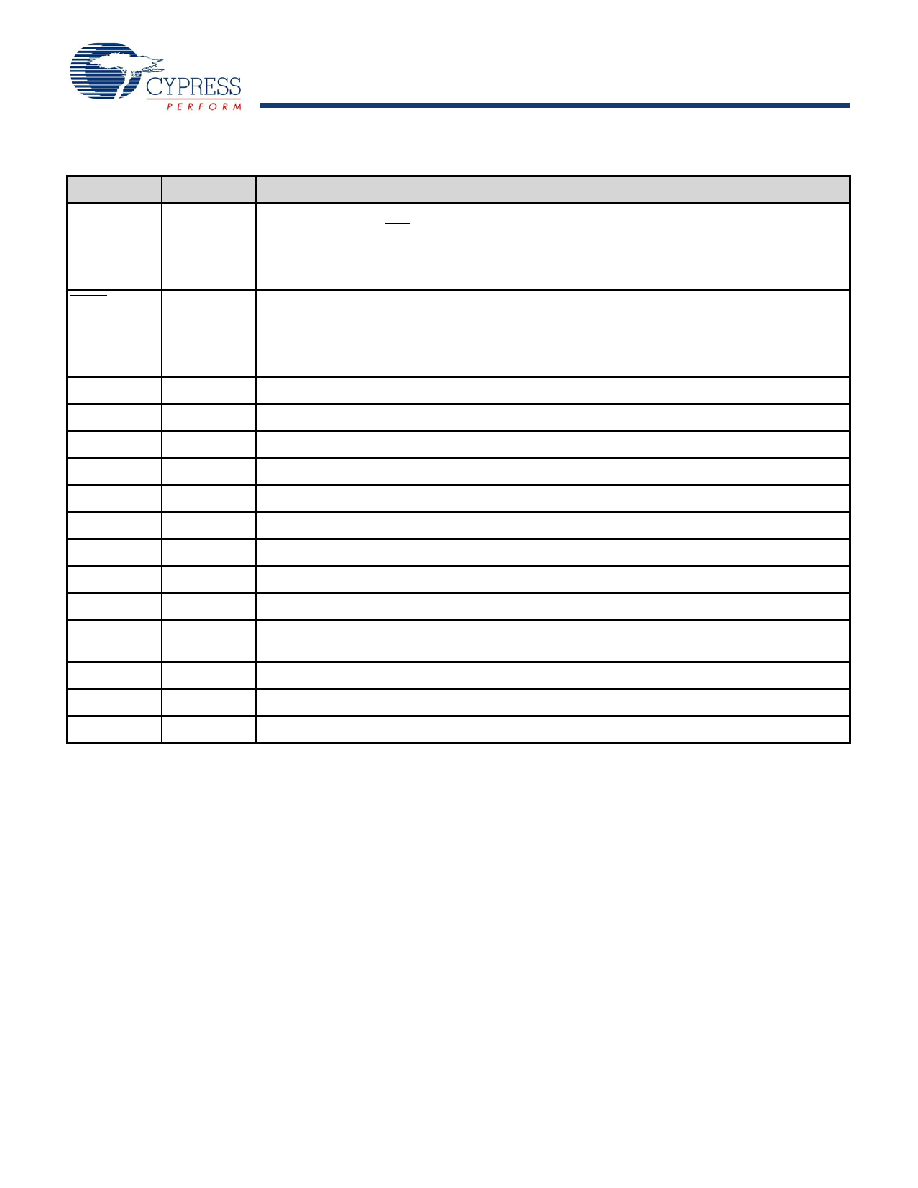

ZQ

Input

Output Impedance Matching Input. This input is used to tune the device outputs to the system data

bus impedance. CQ, CQ, and Q[x:0] output impedance are set to 0.2 x RQ, where RQ is a resistor

connected between ZQ and ground. Alternatively, this pin can be connected directly to VDDQ, which

enables the minimum impedance mode. This pin cannot be connected directly to GND or left uncon-

nected.

DOFF

Input

DLL Turn Off

Active LOW. Connecting this pin to ground turns off the DLL inside the device. The

timings in the DLL turned off operation is different from those listed in this data sheet. For normal

operation, this pin can be connected to a pull up through a 10K

Ω or less pull up resistor. The device

behaves in DDR-I mode when the DLL is turned off. In this mode, the device can be operated at a

frequency of up to 167 MHz with DDR-I timing.

TDO

Output

TDO for JTAG.

TCK

Input

TCK Pin for JTAG.

TDI

Input

TDI Pin for JTAG.

TMS

Input

TMS Pin for JTAG.

NC

N/A

Not Connected to the Die. Tie to any voltage level.

NC/36M

N/A

Not Connected to the Die. Tie to any voltage level.

NC/72M

N/A

Not Connected to the Die. Tie to any voltage level.

NC/144M

N/A

Not Connected to the Die. Tie to any voltage level.

NC/288M

N/A

Not Connected to the Die. Tie to any voltage level.

VREF

Input-

Reference

Reference Voltage Input. Static input used to set the reference level for HSTL inputs, outputs, and

AC measurement points.

VDD

Power Supply Power Supply Inputs to the Core of the Device.

VSS

Ground

Ground for the Device.

VDDQ

Power Supply Power Supply Inputs for the Outputs of the Device.

Pin Definitions (continued)

Pin Name

IO

Pin Description

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C1177V18-333BZXI | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1170V18 | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1177V18 | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1215H-100AXC | 1-Mbit (32K x 32) Pipelined Sync SRAM |

| CY7C1215H-100AXI | 1-Mbit (32K x 32) Pipelined Sync SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C1214F-100AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1214F-100ACT | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1215F-166AC | 制造商:Rochester Electronics LLC 功能描述:1MB (32K X 32) 3.3V PIPELINE SCD - Bulk 制造商:Cypress Semiconductor 功能描述: |

| CY7C1215H-166AXC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC SGL 3.3V 1MBIT 32KX32 3.5NS 100TQFP - Bulk |

| CY7C1217H-133AXC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC QUAD 3.3V 1.125MBIT 32KX36 7.5NS 100TQFP - Bulk |

发布紧急采购,3分钟左右您将得到回复。