- 您现在的位置:买卖IC网 > PDF目录1915 > DS26900LN+ (Maxim Integrated Products)IC JTAG MUX/SWITCH 144-LQFP PDF资料下载

参数资料

| 型号: | DS26900LN+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 39/49页 |

| 文件大小: | 0K |

| 描述: | IC JTAG MUX/SWITCH 144-LQFP |

| 标准包装: | 90 |

| 系列: | * |

| 功能: | * |

| 电压电源: | 单电源 |

| 电压 - 电源,单路/双路(±): | 3.14 V ~ 3.47 V |

| 电流 - 电源: | * |

| 工作温度: | * |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

__________________________________________________________________________________________DS26900

44

11. AC Timing

Unless otherwise noted, all timing numbers assume 20pF test load on output signals, 40pF test load on bus

signals.

11.1 Switch TAP Controller Interface Timing

Table 11-1. Switch TAP Controller Interface Timing

PARAMETER

SYMBOL

MIN

TYP

MAX

UNITS

NOTES

ETCK, TCK1, TCK2 Clock Period

t1

25

ns

30% DC

ETCK, TCK1, TCK2 Clock Low Time

t2

17.5

ns

ETCK, TCK1, TCK2 Clock High Time

t3

7.5

ns

ETCK to ETDI, ETMS Setup Time

TCK1 to TDI1, TMS1 Setup Time

TCK2 to TDI2, TMS2 Setup Time

t4

3

ns

ETCK to ETDI, ETMS Hold Time

TCK1 to TDI1, TMS1 Hold Time

TCK2 to TDI2, TMS2 Hold Time

t5

3

ns

ETCK to ETDO Delay

TCK1 to TDO1 Delay

TCK2 to TDO2 Delay

t6

15

ns

ETCK to ETDO High-Impedance Delay

TCK1 to TDO1 High-Impedance Delay

TCK2 to TDO2 High-Impedance Delay

t7

17.5

ns

Note 1:

TCK should be stopped low.

Note 2:

Interface timing in Table 11-1 is to/from the arbitrated master.

Note 3:

TCK corresponds to each master port clock when being used to configure the core JTAG controller, e.g., ETCK or TCK1 or TCK2.

Note 4:

TDI, TMS correspond to the master port TDI, TMS when being used to configure the core JTAG controller, e.g., ETDI, ETMS or

TDI1, TMS1 or TDI2, TMS2.

Note 5:

TDO corresponds to the master port TDO when being used to configure the core JTAG controller, e.g., ETDO or TDO1 or TDO2.

Note 6:

The configuration signals (

TRST1, TRST2, ECFG) and the master request signals (TMREQ1, TMREQ2, EREQ) are asynchronous.

TCK, TDI, TMS should be low when switching masters to avoid the possibility of glitching the secondary port whose address is in

the Secondary Port Selection Register (SPSR). Another method to avoid glitching the secondary port is to set the Secondary Port

Selection Register (SPSR) to 00000 when changing the arbitrated master.

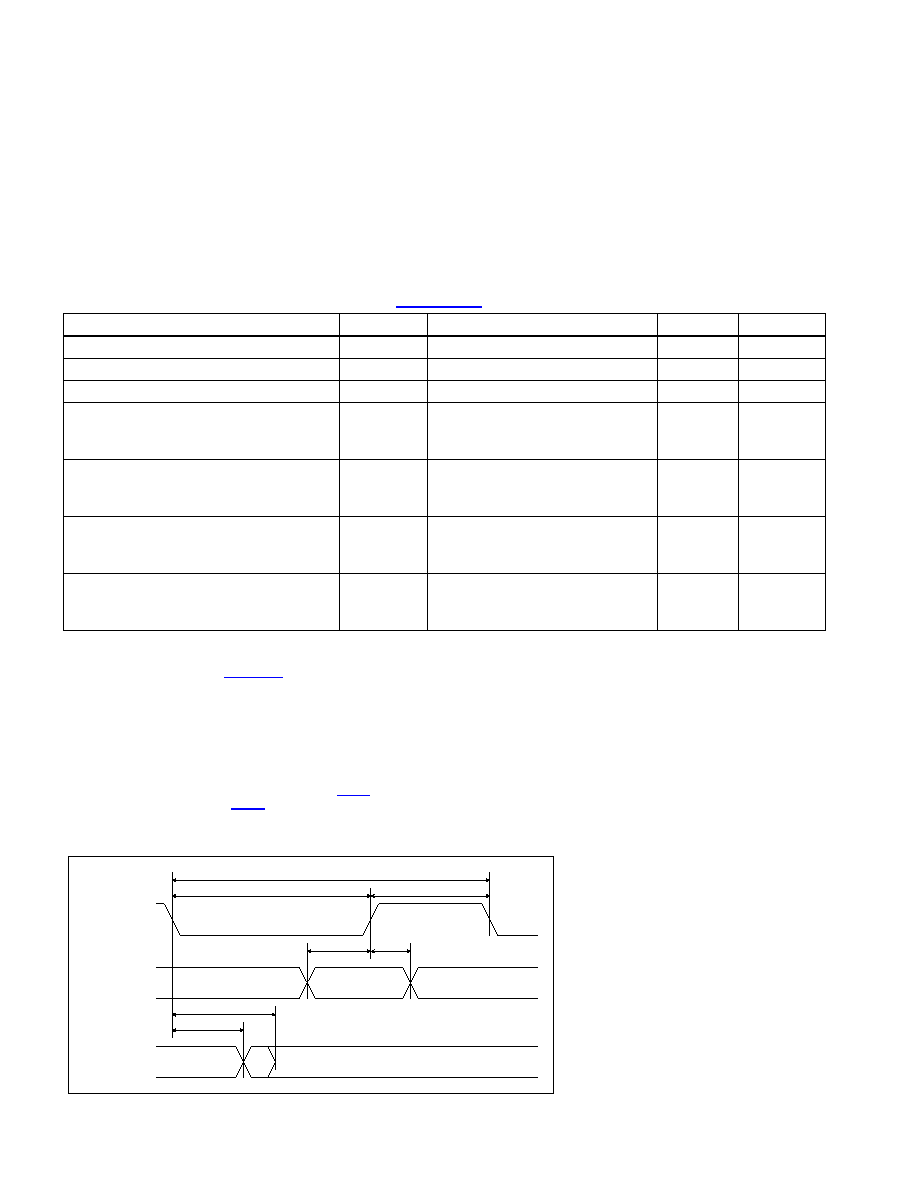

Figure 11-1. Switch TAP Controller Interface Timing Diagram

ETCK

TCK1

TCK2

ETDO

TDO1

TDO2

T2

T3

T1

T4

ETDI, ETMS

TDI1, TMS1

TDI2, TMS2

T5

T6

T7

相关PDF资料 |

PDF描述 |

|---|---|

| DS275E/T&R | IC TXRX LINE-PWR RS232 14-TSSOP |

| DS276S | IC TXRX LOW POWER RS-232 8-SOIC |

| DS2890P-000+T&R | IC POT DIGITAL 1-WIRE 100K 6TSOC |

| DS28CM00R-A00+T | IC SILICON SERIAL NUMBER SOT23-5 |

| DS30EA101SQE/NOPB | IC CABLE EQUALIZER 16LLP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS26900LN+ | 功能描述:多路器开关 IC JTAG MUX RoHS:否 制造商:Texas Instruments 通道数量:1 开关数量:4 开启电阻(最大值):7 Ohms 开启时间(最大值): 关闭时间(最大值): 传播延迟时间:0.25 ns 工作电源电压:2.3 V to 3.6 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UQFN-16 |

| DS26900N+ | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:JTAG Multiplexer/Switch |

| DS26C31 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:CMOS QUAD TRI-STATE DIFFERENTIAL LINE DRIVER |

| DS26C31 DIE | 制造商:Texas Instruments 功能描述: |

| DS26C31_BBA3026X WAF | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。