- 您现在的位置:买卖IC网 > PDF目录10993 > DS3170N+ (Maxim Integrated Products)IC TXRX DS3/E3 100-CSBGA PDF资料下载

参数资料

| 型号: | DS3170N+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 227/230页 |

| 文件大小: | 0K |

| 描述: | IC TXRX DS3/E3 100-CSBGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 640 |

| 功能: | 单芯片收发器 |

| 接口: | DS3,E3 |

| 电路数: | 1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 电流 - 电源: | 120mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LBGA,CSBGA |

| 供应商设备封装: | 100-CSBGA(11x11) |

| 包装: | 托盘 |

| 包括: | DS3 调帧器,E3 调帧器,HDLC 控制器,芯片内 BERT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页当前第227页第228页第229页第230页

DS3170 DS3/E3 Single-Chip Transceiver

96 of 230

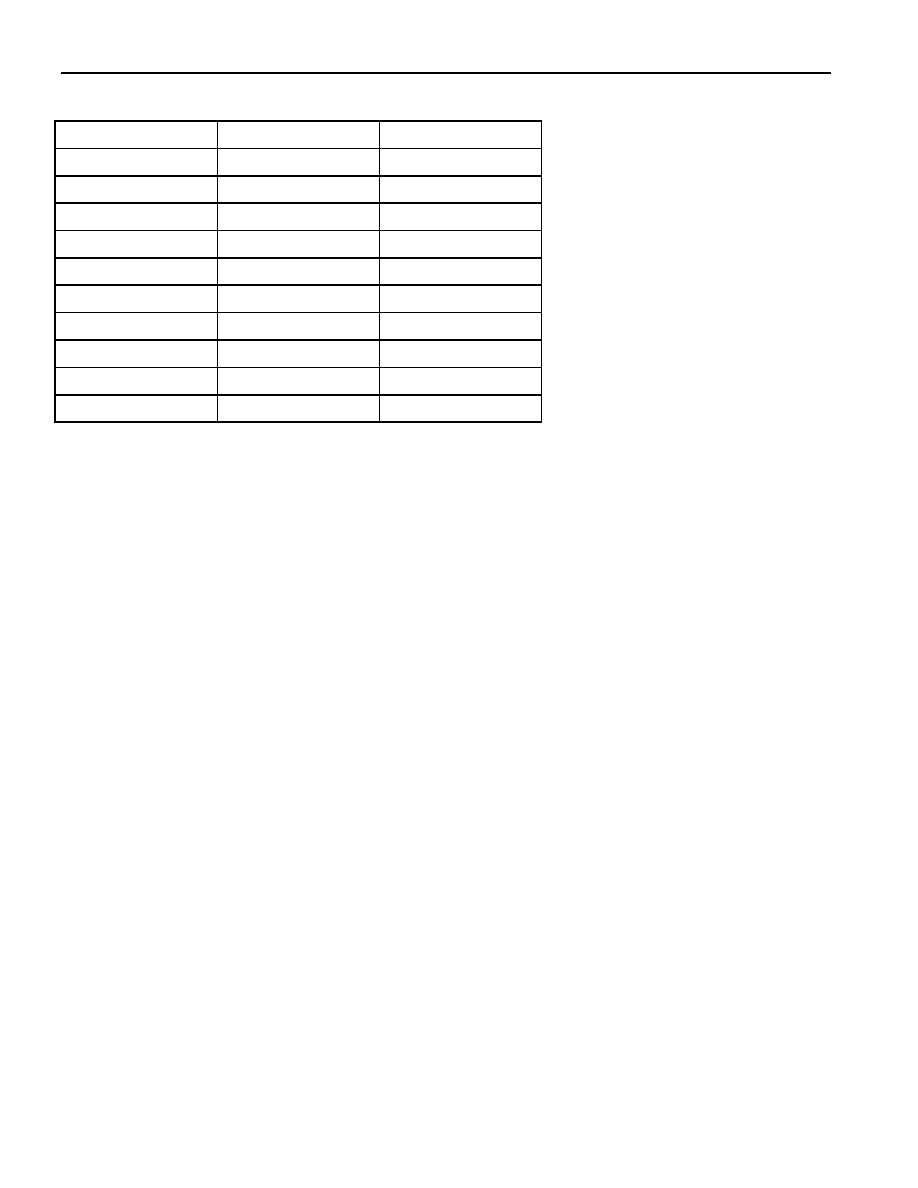

Table 10-30. Payload Label Match Status

EXPECTED

RECEIVED

STATUS

000

Match

000

001

Mismatch

000

XXX

Mismatch

001

000

Mismatch

001

Match

001

XXX

Match

XXX

000

Mismatch

XXX

001

Match

XXX

Match

XXX

YYY

Mismatch

XXX and YYY equal any value other than 000 or 001; XXX

≠ YYY.

The multiframe indicator and timing marker bits (sixth, seventh, and eighth bits of the MA byte) can be integrated

and stored in three register bits or extracted, integrated, and stored in four register bits. The bits (three or four) are

stored with a change indication. The multiframe indicator and timing marker storage type is programmable

(integrated or extracted). When the multiframe indicator and timing marker bits are integrated, the last three bits of

the MA byte are integrated and stored in three register bits. When the multiframe indicator and timing marker bits

are extracted, four timing source indicator bits are transferred in a four-frame multiframe, MSB first. The multiframe

indicator bits (sixth and seventh bits of the MA byte) identify the phase of the multiframe (00, 01, 10, or 11). The

timing marker bit (eighth bit of the MA byte) contains the timing source indicator bit indicated by the multiframe

indicator bits (first, second, third, or fourth bit respectively). The four timing source indicator bits are extracted from

the multiframe, integrated, and stored in four register bits with unstable and change indications.

The NR byte is integrated and stored in a register along with a change indication, it is sent to the receive FEAC

controller, and it can be sent to the receive HDLC controller. The byte sent to the receive HDLC controller is

programmable (NR or GC).

The GC byte is integrated and stored in a register along with a change indication, and can be sent to the receive

HDLC controller. The byte sent to the receive HDLC controller is programmable (NR or GC).

10.6.8.10 Receive G.832 Downstream AIS Generation

Downstream G.832 E3 AIS can be automatically generated on an OOF, LOS, or AIS condition or manually

inserted. If automatic downstream AIS is enabled, downstream AIS is inserted when an LOS, OOF, or AIS

condition is declared. Automatic downstream AIS is programmable (on or off). If manual downstream AIS insertion

is enabled, downstream AIS is inserted. Manual downstream AIS insertion is programmable (on or off).

Downstream AIS is removed when all OOF, LOS, and AIS conditions are terminated and manual downstream AIS

insertion is disabled. RPDT will be forced to all ones during downstream AIS.

10.7 HDLC Overhead Controller

10.7.1 General Description

The DS3170 device contains a built-in HDLC controller with 256 byte FIFOs for insertion/extraction of DS3 PMDL,

G.751 Sn bit and G.832 NR/GC bytes.

The HDLC Overhead Controller demaps HDLC overhead packets from the DS3/E3 data stream in the receive

direction and maps HDLC packets into the DS3/E3 data stream in the transmit direction.

The receive direction performs packet processing and stores the packet data in the FIFO. It removes packet data

from the FIFO and outputs the packet data to the microprocessor via the register interface.

The transmit direction inputs the packet data from the microprocessor via the register interface and stores the

packet data in the FIFO. It removes the packet data from the FIFO and performs packet processing.

相关PDF资料 |

PDF描述 |

|---|---|

| DS2151QB | IC TXRX T1 1-CHIP 5V LP 44-PLCC |

| DS21Q58LN+ | IC TXRX E1 QUAD 3.3V 100LQFP |

| DS26504LN+ | IC T1/E1/J1 64KCC ELEMENT 64LQFP |

| DS21352G | IC TXRX T1 1-CHIP 3.3V 100-BGA |

| DS2174QN+T&R | IC BERT ENHANCED 44-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3170N+ | 功能描述:网络控制器与处理器 IC DS3/E3 Single-Chip Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS3170N+T&R | 制造商:Maxim Integrated Products 功能描述:SINGLE PORT DS3/E3 SCT T&R IND LF - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC TXRX DS3/E3 100CSBGA |

| DS3170N+T&R | 功能描述:网络控制器与处理器 IC DS3/E3 Single-Chip Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS3171 | 功能描述:网络控制器与处理器 IC Single DS3/E3 Single Chip Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS3171N | 功能描述:网络控制器与处理器 IC Single DS3/E3 Single Chip Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。