- 您现在的位置:买卖IC网 > PDF目录16559 > EV-ADF4153SD1Z (Analog Devices Inc)BOARD EVAL FOR ADF4153SD1Z PDF资料下载

参数资料

| 型号: | EV-ADF4153SD1Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADF4153SD1Z |

| 标准包装: | 1 |

| 系列: | * |

Data Sheet

ADF4153

Rev. F | Page 19 of 24

The programmable modulus is also very useful for multi-

standard applications. If a dual-mode phone requires PDC

and GSM 1800 standards, the programmable modulus is of

great benefit. PDC requires 25 kHz channel step resolution,

whereas GSM 1800 requires 200 kHz channel step resolution.

A 13 MHz reference signal can be fed directly to the PFD.

The modulus is programmed to 520 when in PDC mode

(13 MHz/520 = 25 kHz). The modulus is reprogrammed to

65for GSM 1800 operation (13 MHz/65 = 200 kHz). It is

important that the PFD frequency remains constant (13 MHz).

This allows the user to design one loop filter that can be used in

both setups without running into stability issues. It is the ratio

of the RF frequency to the PFD frequency that affects the loop

design. By keeping this relationship constant, the same loop

filter can be used in both applications.

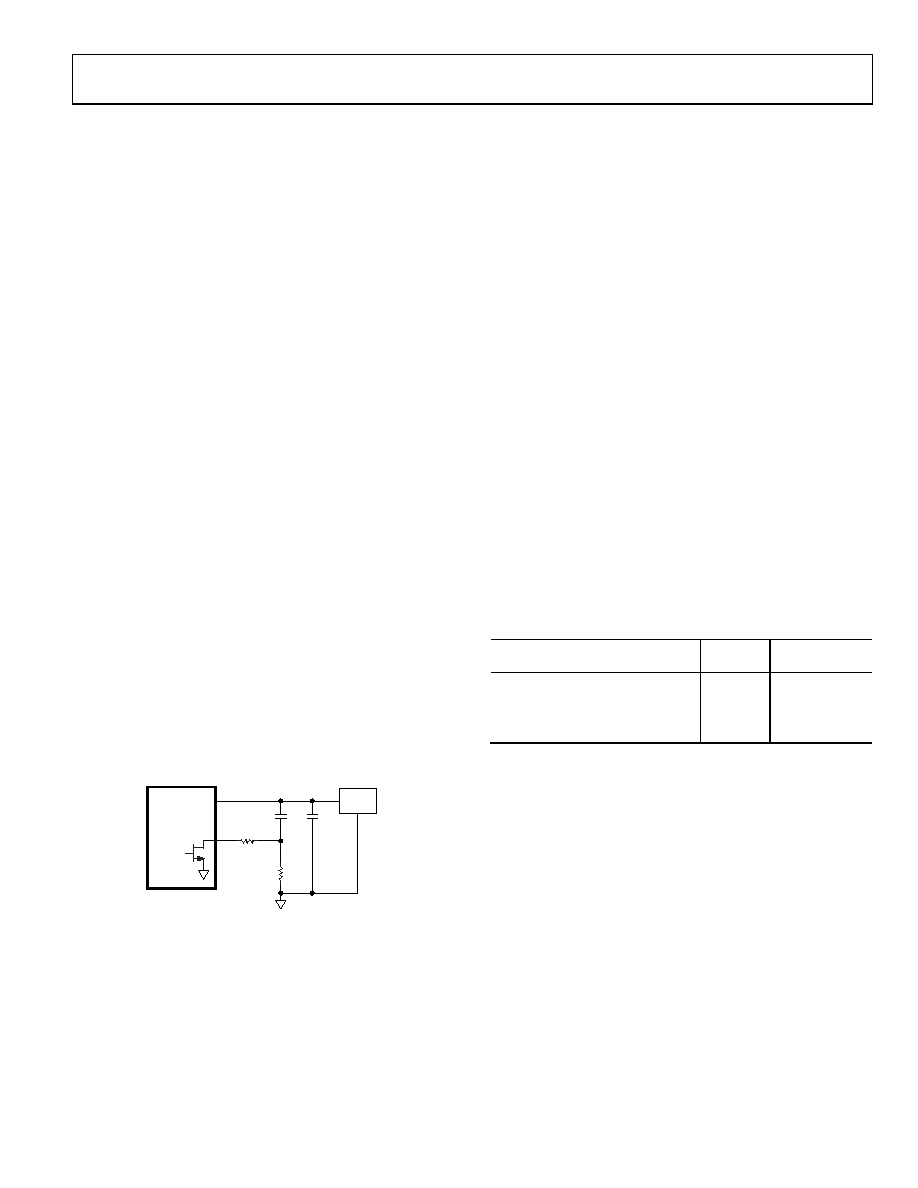

FASTLOCK WITH SPURIOUS OPTIMIZATION

As mentioned in the Noise and Spur Mode section, the part can

be optimized for spurious performance. However, in fastlocking

applications, the loop bandwidth needs to be wide, and

therefore the filter does not provide much attenuation of the

spurs. The programmable charge pump can be used to get

around this issue. The filter is designed for a narrow-loop

bandwidth so that steady-state spurious specifications are met.

This is designed using the lowest charge pump current setting.

To implement fastlock during a frequency jump, the charge

pump current is set to the maximum setting for the duration of

the jump by asserting the fastlock bit in the N divider register.

This widens the loop bandwidth, which improves lock time. To

maintain loop stability while in wide bandwidth mode, the loop

filter needs to be modified. This is achieved by switching in a

resistor (R1A) in parallel with the damping resistor in the loop

filter (see Figure 16). MUXOUT needs to be set to the fastlock

switch to use the internal switch. For example, if the charge

pump current is increased by 16, the damping resistor, R1,

needs to be decreased by while in wide bandwidth mode.

ADF4153

VCO

C2

C1

CP

FL

MUXOUT

R1

R1A

03685-

029

Figure 16. ADF4153 with Fastlock

The value of R1A is then chosen so that the total parallel

resistance of R1 and R1A equals 1/4 of R1 alone. This gives

an overall 4× increase in loop bandwidth, while maintaining

stability in wide bandwidth mode.

When the PLL has locked to the new frequency, the charge

pump is again programmed to the lowest charge pump current

setting by setting the fastlock bit to 0. The internal switch opens

and the damping resistor reverts to its original value. This

narrows the loop bandwidth to its original cutoff frequency

to allow better attenuation of the spurs than the wide-loop

bandwidth.

SPUR MECHANISMS

The following section describes the three different spur mechan-

isms that arise with a fractional-N synthesizer and how to

minimize them in the ADF4153.

Fractional Spurs

The fractional interpolator in the ADF4153 is a third-order Σ-Δ

modulator (SDM) with a modulus (MOD) that is programmable

to any integer value from 2 to 4095. In low spur mode (dither

enabled), the minimum allowed value of MOD is 50. The SDM

is clocked at the PFD reference rate (FPFD) that allows PLL

output frequencies to be synthesized at a channel step

resolution of FPFD/MOD.

In lowest noise mode and low noise and spur mode (dither off),

the quantization noise from the Σ-Δ modulator appears as frac-

tional spurs. The interval between spurs is FPFD/L, where L is the

repeat length of the code sequence in the digital Σ-Δ modulator.

For the third-order modulator used in the ADF4153, the repeat

length depends on the value of MOD, as shown in Table 11.

Table 11. Fractional Spurs with Dither Off

Condition (Dither Off)

Repeat

Length

Spur Interval

If MOD is divisible by 2, but not 3

2 × MOD

Channel step/2

If MOD is divisible by 3, but not 2

3 × MOD

Channel step/3

If MOD is divisible by 6

6 × MOD

Channel step/6

Otherwise

MOD

Channel step

In low spur mode (dither enabled), the repeat length is

extended to 221 cycles, regardless of the value of MOD, which

makes the quantization error spectrum look like broadband

noise. This can degrade the in-band phase noise at the PLL

output by as much as 10 dB. Therefore, for lowest noise, dither

off is a better choice, particularly when the final loop BW is low

enough to attenuate even the lowest frequency fractional spur.

Integer Boundary Spurs

Another mechanism for fractional spur creation is interactions

between the RF VCO frequency and the reference frequency.

When these frequencies are not integer related (which is the

point of a fractional-N synthesizer), spur sidebands appear on

the VCO output spectrum at an offset frequency that corresponds

to the beat note or difference frequency between an integer

multiple of the reference and the VCO frequency.

These spurs are attenuated by the loop filter and are more

noticeable on channels close to integer multiples of the

reference where the difference frequency can be inside the

loop bandwidth, therefore, the name integer boundary spurs.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX5059EUI+T | IC DRVR SYNC RECT 28-TSSOP |

| TCM809TVNB713 | IC RESET MONITOR 3.08V SOT23B-3 |

| GMM10DREI | CONN EDGECARD 20POS .156 EYELET |

| A1DXB-2036M | IDC CABLE- AKR20B/AE20M/X |

| H1WXH-1436M | IDC CABLE - HPL14H/AE14M/X |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EV-ADF4156SD1Z | 功能描述:BOARD EVAL FOR ADF4156 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EV-ADF4157SD1Z | 功能描述:BOARD EVAL FOR ADF4157 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EV-ADF4159EB1Z | 制造商:Analog Devices 功能描述:EVALUATION BOARD - Boxed Product (Development Kits) 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADF4159 |

| EV-ADF4159EB2Z | 制造商:Analog Devices 功能描述:13GHZFRAC-NPLL+ADF55XXVCO+3VADM - Boxed Product (Development Kits) |

| EV-ADF4159EB3Z | 制造商:Analog Devices 功能描述:EVALUATIONBOARD - Boxed Product (Development Kits) 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADF4159 制造商:Analog Devices 功能描述:Clock & Timer Development Tools ADF4159 EVAL BRD |

发布紧急采购,3分钟左右您将得到回复。