- 您现在的位置:买卖IC网 > PDF目录16559 > EV-ADF4153SD1Z (Analog Devices Inc)BOARD EVAL FOR ADF4153SD1Z PDF资料下载

参数资料

| 型号: | EV-ADF4153SD1Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADF4153SD1Z |

| 标准包装: | 1 |

| 系列: | * |

Data Sheet

ADF4153

Rev. F | Page 9 of 24

CIRCUIT DESCRIPTION

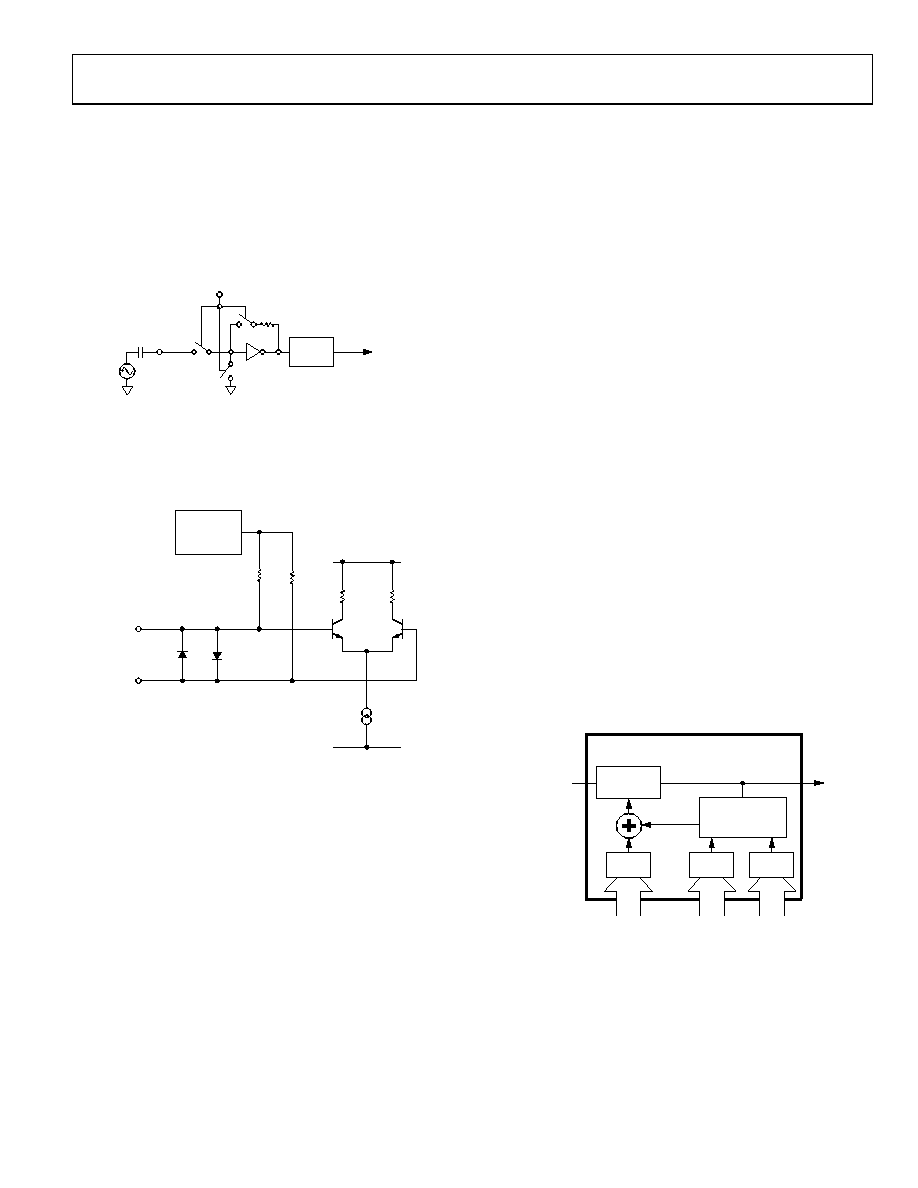

REFERENCE INPUT SECTION

The reference input stage is shown in Figure 11. SW1 and SW2

are normally closed switches. SW3 is normally open. When

power-down is initiated, SW3 is closed and SW1 and SW2 are

opened. This ensures that there is no loading of the REFIN pin

on power-down.

03685-

027

BUFFER

TO R COUNTER

REFIN

100k

NC

SW2

SW3

NO

NC

SW1

POWER-DOWN

CONTROL

Figure 11. Reference Input Stage

RF INPUT STAGE

The RF input stage is shown in Figure 12. It is followed by a

2-stage limiting amplifier to generate the current-mode logic

(CML) clock levels needed for the prescaler.

BIAS

GENERATOR

1.6V

AGND

AVDD

2k

RFINB

RFINA

03685-

015

Figure 12. RF Input Stage

RF INT DIVIDER

The RF INT CMOS counter allows a division ratio in the PLL

feedback counter. Division ratios from 31 to 511 are allowed.

INT, FRAC, MOD, AND R RELATIONSHIP

The INT, FRAC, and MOD values, in conjunction with the

R counter, make it possible to generate output frequencies that

are spaced by fractions of the phase frequency detector (PFD).

See the RF Synthesizer: A Worked Example section for more

information. The RF VCO frequency (RFOUT) equation is

RFOUT = FPFD × (INT + (FRAC/MOD))

(1)

where:

RFOUT is the output frequency of the external voltage controlled

oscillator (VCO).

INT is the preset divide ratio of the binary 9-bit counter (31

to 511).

MOD is the preset fractional modulus (2 to 4095).

FRAC is the numerator of the fractional division (0 to MOD 1).

The PFD frequency is given by:

FPFD = REFIN × (1 + D)/R

(2)

where:

REFIN is the reference input frequency.

D is the REFIN doubler bit.

R is the preset divide ratio of the binary 4-bit programmable

reference counter (1 to 15).

RF R COUNTER

The 4-bit RF R counter allows the input reference frequency

(REFIN) to be divided down to produce the reference clock to

the PFD. Division ratios from 1 to 15 are allowed.

THIRD-ORDER

FRACTIONAL

INTERPOLATOR

FRAC

VALUE

MOD

REG

INT

REG

RF N DIVIDER

N = INT + FRAC/MOD

FROM RF

INPUT STAGE

TO PFD

N-COUNTER

03685-

016

Figure 13. RF N Divider

相关PDF资料 |

PDF描述 |

|---|---|

| MAX5059EUI+T | IC DRVR SYNC RECT 28-TSSOP |

| TCM809TVNB713 | IC RESET MONITOR 3.08V SOT23B-3 |

| GMM10DREI | CONN EDGECARD 20POS .156 EYELET |

| A1DXB-2036M | IDC CABLE- AKR20B/AE20M/X |

| H1WXH-1436M | IDC CABLE - HPL14H/AE14M/X |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EV-ADF4156SD1Z | 功能描述:BOARD EVAL FOR ADF4156 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EV-ADF4157SD1Z | 功能描述:BOARD EVAL FOR ADF4157 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EV-ADF4159EB1Z | 制造商:Analog Devices 功能描述:EVALUATION BOARD - Boxed Product (Development Kits) 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADF4159 |

| EV-ADF4159EB2Z | 制造商:Analog Devices 功能描述:13GHZFRAC-NPLL+ADF55XXVCO+3VADM - Boxed Product (Development Kits) |

| EV-ADF4159EB3Z | 制造商:Analog Devices 功能描述:EVALUATIONBOARD - Boxed Product (Development Kits) 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADF4159 制造商:Analog Devices 功能描述:Clock & Timer Development Tools ADF4159 EVAL BRD |

发布紧急采购,3分钟左右您将得到回复。