- 您现在的位置:买卖IC网 > PDF目录16871 > EVAL-AD5522EBDZ (Analog Devices Inc)BOARD EVAL FOR 14X14MM AD5522 PDF资料下载

参数资料

| 型号: | EVAL-AD5522EBDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 44/64页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR 14X14MM AD5522 |

| 标准包装: | 1 |

| 主要目的: | 测试与测量,参数测量单元(PMU) |

| 已用 IC / 零件: | AD5522 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Data Sheet

AD5522

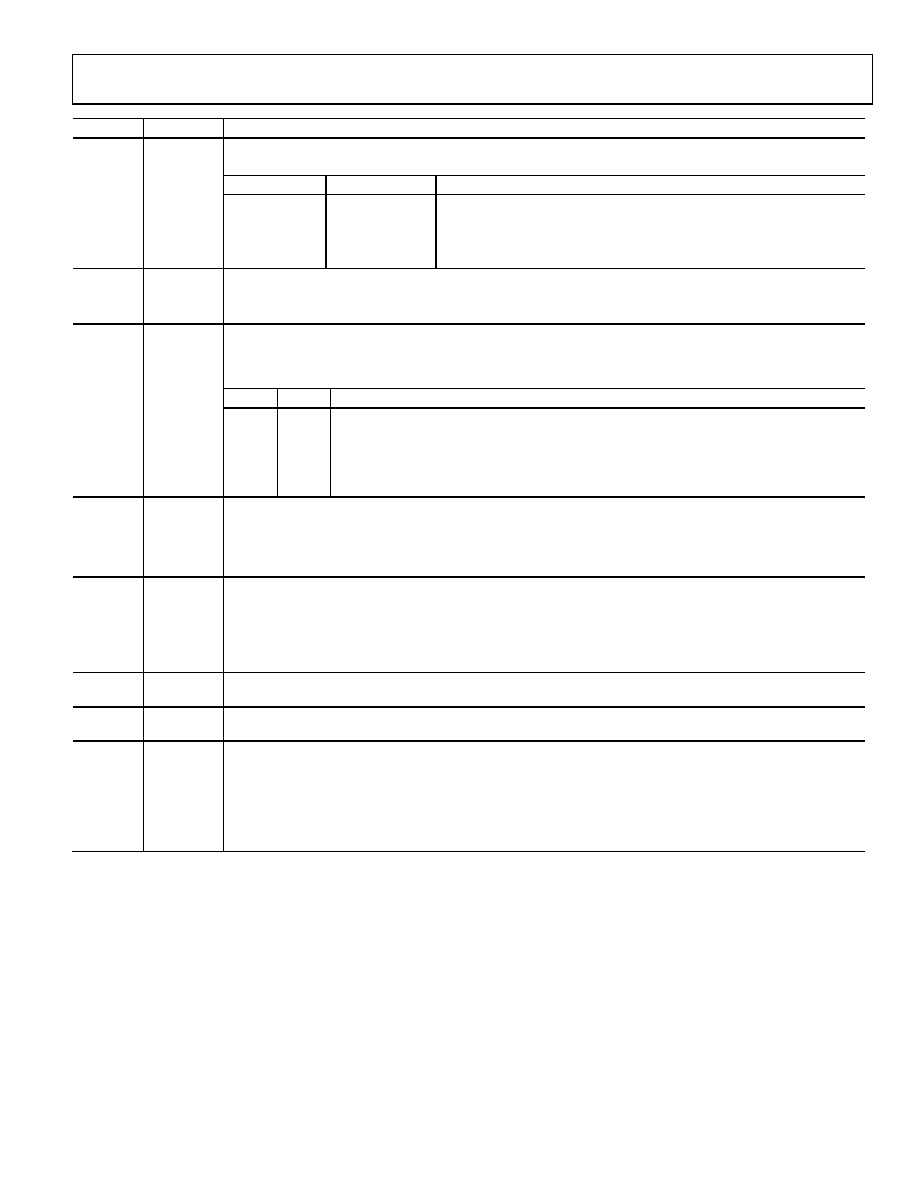

Rev. E | Page 49 of 64

Bit

Bit Name

Description

14

MEAS1

The MEAS1 and MEAS0 bits specify the required measure mode, allowing the MEASOUTx line to be disabled,

connected to the temperature sensor, or enabled for measurement of current or voltage.

13

MEAS0

MEAS1

MEAS0

Action

0

MEASOUTx is connected to ISENSE

0

1

MEASOUTx is connected to VSENSE

1

0

MEASOUTx is connected to the temperature sensor

1

MEASOUTx is high-Z (SW12 open)

12

FIN

This bit sets the status of the force input (FIN) amplifier.

0 = input of the force amplifier switched to GND.

1 = input of the force amplifier connected to the FIN DAC output.

11

SF0

The SF0 and SS0 bits specify the switching of system force and sense lines to the force and sense paths at the

DUT. The channel to which the system force and system sense lines are connected is set by the PMU3 to PMU0

bits. For correct operation, only one PMU channel should be connected to the SYS_FORCE and SYS_SENSE

paths at any one time.

10

SS0

SF0

SS0

Action

0

SYS_FORCE and SYS_SENSE are high-Z for the selected channel

0

1

SYS_FORCE is high-Z and SYS_SENSE is connected to MEASVHx for the selected channels

1

0

SYS_FORCE is connected to FOHx and SYS_SENSE is high-Z for the selected channel

1

SYS_FORCE is connected to FOHx and SYS_SENSE is connected to MEASVHx for the selected

channel

9

CL

Per-PMU current or voltage clamp enable bit. A logic high enables the clamp function for the selected PMU. The

clamp enable function is also available in the system control register. This dual functionality allows flexible

enabling or disabling of this function. When reading back information about the status of the clamp enable

function on a per-channel basis, the data that was most recently written to the clamp register is available in the

readback word from either the PMU register or the system control register.

8

CPOLH

Comparator output enable bit. By default, the comparator outputs are high-Z on power-on. A logic high enables

the comparator output for the selected PMU. The comparator function CPBIASEN (Bit 13 in the system control

register), must be enabled. The comparator output enable function is also available in the system control register.

This dual functionality allows flexible enabling or disabling of this function. When reading back information about

the status of the comparator enable function, the data that was most recently written to the comparator status

register is available in the readback word from either the PMU register or the system control register.

7

Compare

V/I

A logic high selects the compare voltage function; a logic low selects the compare current function.

6

Clear

To clear or reset a latched alarm bit and pin (temperature, guard, or clamp), write a 1 to this bit. This bit applies

to latched alarm conditions (clamp and guard) on all four PMU channels.

5

Unused

Unused bits. Set to 0.

4

3

2

1

0 (LSB)

1

Writing 101 in Bit 17 to Bit 15 disables the always on mode for the external current range buffer. Use with FV mode (FORCE1 = FORCE0 = 0) only. To complete the

disabling of the always on mode, the PMU channel is placed into high-Z mode and the external current range buffer is returned to its default operation (off).

2

Writing 110 in Bit 17 to Bit 15 places the external current range buffer into always on mode. In this mode, the buffer is always active with no regard to the selected current

range. The always on mode is intended for use where an external high current stage is being used for a current drive in excess of ±80 mA; having the internal stage

always on should help to eliminate timing concerns when transitioning between this current range and other ranges. When first enabling the always on mode, use it in

conjunction with FV mode (FORCE1 = FORCE0 = 0); the device now enables the external current range buffer. The 110 code also places the device into high-Z mode

(necessary to complete the enabling function). To return to an FV or FI operating mode, select the appropriate mode and current range. The external range sense

resistor is connected to an MI circuit only when the external current range address is selected (C2 to C0 are set to 100). The default operation at power-on is disabled

(or off).

相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-AD5520EBZ | BOARD EVAL FOR AD5520 |

| MAX6198AESA+T | IC VREF SERIES PREC 4.096V 8SOIC |

| QPI-5-EVAL1 | EVALUATION BOARD FOR QPI-5 |

| H6MMH-4006M | DIP CABLE - HDM40H/AE40M/HDM40H |

| QPO-2-EVAL1 | EVALUATION BOARD FOR QPO-2 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5522EBUZ | 功能描述:BOARD EVAL FOR 12X12MM AD5522 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD5532EB | 制造商:AD 制造商全称:Analog Devices 功能描述:32-Channel Infinite Sample-and-Hold |

| EVAL-AD5532EBZ | 功能描述:BOARD EVAL FOR AD5532 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5532HSEBZ | 功能描述:BOARD EVAL FOR AD5532HS RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5533EB | 制造商:AD 制造商全称:Analog Devices 功能描述:32-Channel Precision Infinite Sample-and-Hold |

发布紧急采购,3分钟左右您将得到回复。