- 您现在的位置:买卖IC网 > PDF目录16848 > EVAL-ADAU1761Z (Analog Devices Inc)BOARD EVAL FOR ADAU1761 PDF资料下载

参数资料

| 型号: | EVAL-ADAU1761Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 54/92页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADAU1761 |

| 标准包装: | 1 |

| 系列: | SigmaDSP® |

| 主要目的: | 音频编解码器 |

| 嵌入式: | 是,DSP |

| 已用 IC / 零件: | ADAU1761 |

| 主要属性: | 立体声,24 位,8 ~ 96 kHz 采样率,GUI 工具 |

| 次要属性: | I²C 和 GPIO 接口,2 差分和 1 个立体声单端模拟输入和输出 |

| 已供物品: | 2 个板,线缆,CD |

| 产品目录页面: | 776 (CN2011-ZH PDF) |

| 相关产品: | ADAU1761BCPZ-RL-ND - IC SIGMADSP CODEC PLL 32LFCSP ADAU1761BCPZ-R7-ND - IC SIGMADSP CODEC PLL 32LFCSP ADAU1761BCPZ-ND - IC SIGMADSP CODEC PLL 32LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页当前第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADAU1761

Rev. C | Page 58 of 92

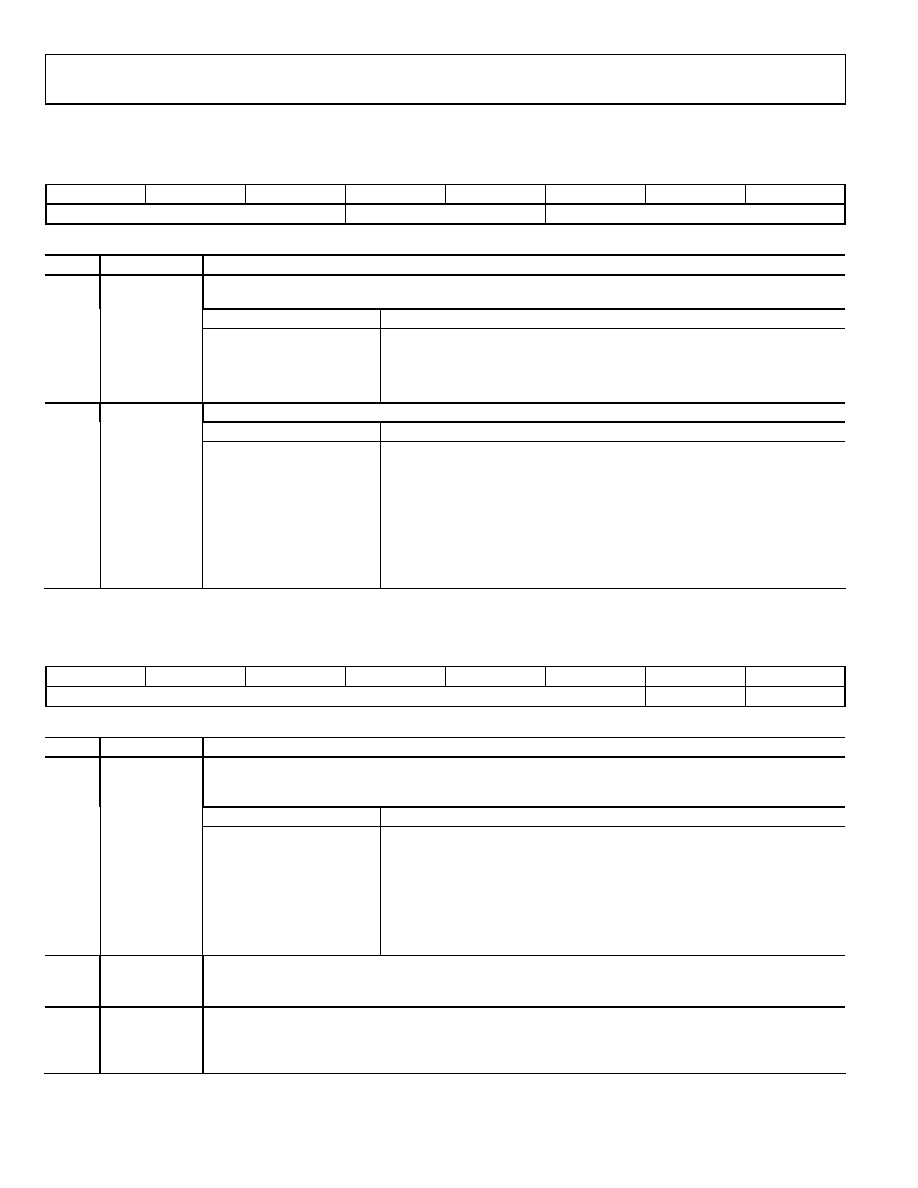

R7: Record Mixer Right (Mixer 2) Control 1, 16,397 (0x400D)

This register controls the gain boost of the right channel differential PGA input and the gain for the right channel auxiliary input in the

record path. The right channel record mixer is referred to as Mixer 2.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reserved

RDBOOST[1:0]

MX2AUXG[2:0]

Table 41. Record Mixer Right (Mixer 2) Control 1 Register

Bits

Bit Name

Description

[4:3]

RDBOOST[1:0]

Right channel differential PGA input gain boost, input to Mixer 2. The right differential input uses the RINP

(positive signal) and RINN (negative signal) pins.

Setting

Gain Boost

00

Mute (default)

01

0 dB

10

20 dB

11

Reserved

[2:0]

MX2AUXG[2:0]

Right single-ended auxiliary input gain from the RAUX pin in the record path, input to Mixer 2.

Setting

Auxiliary Input Gain

000

Mute (default)

001

12 dB

010

9 dB

011

6 dB

100

3 dB

101

0 dB

110

3 dB

111

6 dB

R8: Left Differential Input Volume Control, 16,398 (0x400E)

This register enables the differential path and sets the volume control for the left differential PGA input.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

LDVOL[5:0]

LDMUTE

LDEN

Table 42. Left Differential Input Volume Control Register

Bits

Bit Name

Description

[7:2]

LDVOL[5:0]

Left channel differential PGA input volume control. The left differential input uses the LINP (positive signal) and

LINN (negative signal) pins. Each step corresponds to a 0.75 dB increase in gain. See Table 92 for a complete list

of the volume settings.

Setting

Volume

000000

12 dB (default)

000001

11.25 dB

…

010000

0 dB

…

111110

34.5 dB

111111

35.25 dB

1

LDMUTE

Left differential input mute control.

0 = mute (default).

1 = unmute.

0

LDEN

Left differential PGA enable. When enabled, the LINP and LINN pins are used as a full differential pair. When

disabled, these two pins are configured as two single-ended inputs with the signals routed around the PGA.

0 = disabled (default).

1 = enabled.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX6174BASA+ | IC VREF SERIES PREC 4.096V 8SOIC |

| GSC06DRXI-S734 | CONN EDGECARD 12POS DIP .100 SLD |

| 0982660987 | CBL 29PS 0.5MM JMPR TYPE A 1.18" |

| SRR5028-680Y | INDUCTOR POWER 68UH 0.62A SMD |

| ADN8831ACPZ-REEL7 | IC THERMO COOLER CTRLR 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADAU1781Z | 功能描述:BOARD EVAL FOR ADAU1781 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:SigmaDSP® 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-ADAU1962AZ | 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADAU1962A - Boxed Product (Development Kits) 制造商:Analog Devices 功能描述:Eval Board for ADAU1962A |

| EVAL-ADAU1966AZ | 制造商:Analog Devices 功能描述:EVAL BOARD FOR ADAU1962A - Boxed Product (Development Kits) |

| EVAL-ADAU1966Z | 功能描述:BOARD EVAL FOR ADAU1966 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-ADAU1966Z | 制造商:Analog Devices 功能描述:ADAU1966, DAC, SIGMA DELTA, SPI, I2C, EV |

发布紧急采购,3分钟左右您将得到回复。