- 您现在的位置:买卖IC网 > PDF目录16560 > EVAL-ADF4193EBZ2 (Analog Devices Inc)BOARD EVALUATION EB2 FOR ADF4193 PDF资料下载

参数资料

| 型号: | EVAL-ADF4193EBZ2 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/32页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION EB2 FOR ADF4193 |

| 标准包装: | 1 |

| 主要目的: | 计时,频率合成器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ADF4193 |

| 主要属性: | 400 MHz ~ 3.5 GHz,数字式可编程输出相位 |

| 次要属性: | 板不包括环路滤波器和 VCO |

| 已供物品: | 板,缆线,CD |

| 相关产品: | ADF4193BCPZ-ND - IC PLL FREQ SYNTHESIZER 32LFCSP ADF4193BCPZ-RL7-ND - IC PLL FREQ SYNTHESIZER 32LFCSP ADF4193BCPZ-RL-ND - IC PLL FREQ SYNTHESIZER 32LFCSP |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

Data Sheet

ADF4193

Rev. F | Page 11 of 32

THEORY OF OPERATION

The ADF4193 is targeted at GSM base station requirements,

specifically to eliminate the need for ping-pong solutions. It

works based on fast lock, using a wide loop bandwidth during a

frequency change and narrowing the loop bandwidth once

frequency lock is achieved. Widening the loop bandwidth is

achieved by increasing the charge pump current. Switches are

included to change the loop filter component values to maintain

stability with the changing charge pump current. The narrow

loop bandwidth ensures that phase noise and spur specifications

are met. A differential charge pump and loop filter topology are

used to ensure that the fast lock time benefit from widening the

loop bandwidth is maintained when the loop is restored to

narrow bandwidth mode for normal operation.

REFERENCE INPUT SECTION

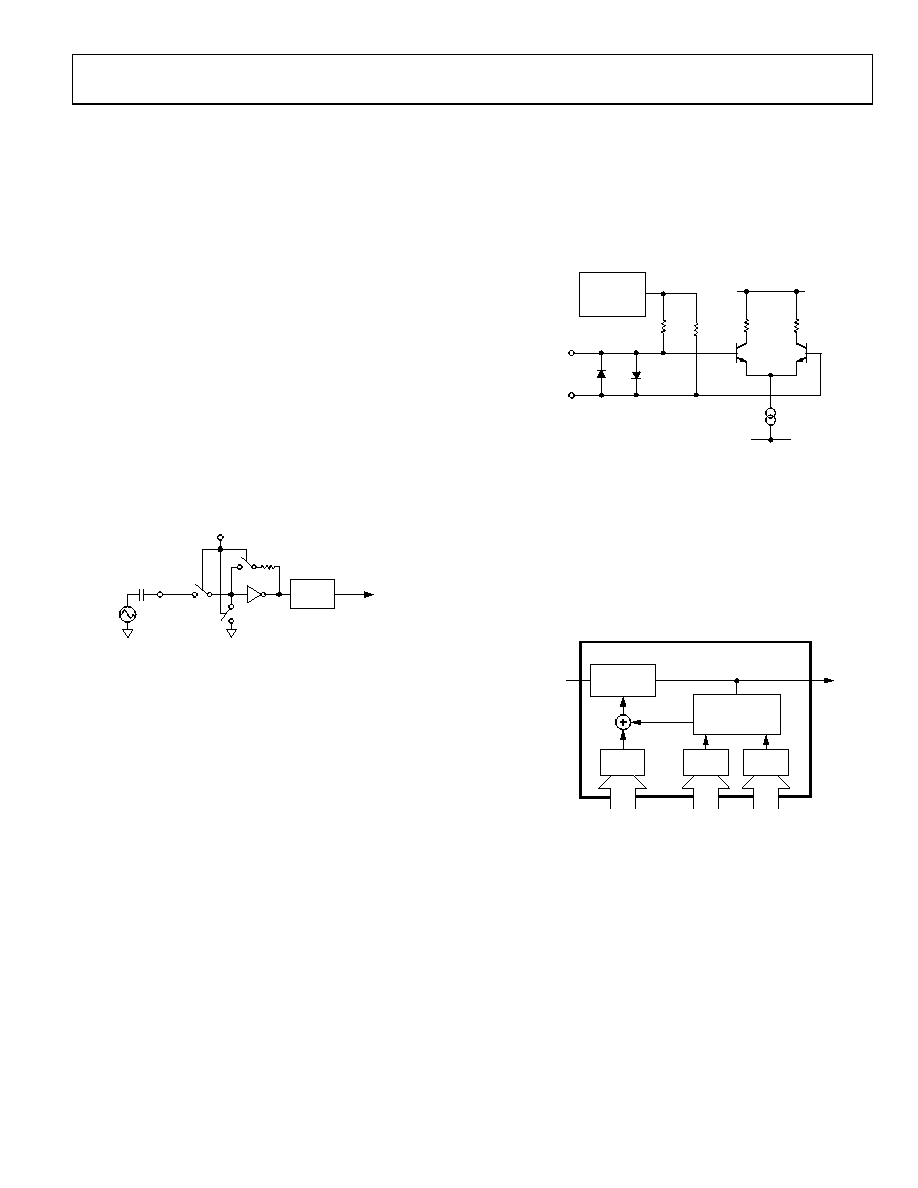

The reference input stage is shown in Figure 20. Switches S1 and

S2 are normally closed, and S3 is normally open. During power-

down, S3 is closed, and S1 and S2 are opened to ensure that

there is no loading of the REFIN pin. The falling edge of REFIN is

the active edge at the positive edge triggered PFD.

05328-016

BUFFER

TO R COUNTER

REFIN

100k

NC

S2

S3

NO

NC

S1

POWER-DOWN

CONTROL

Figure 20. Reference Input Stage

R Counter and Doubler

The 4-bit R counter allows the input reference frequency to be

divided down to produce the reference clock to the phase

frequency detector (PFD). A toggle flip-flop can be optionally

inserted after the R counter to give a further divide-by-2. Using

this option has the additional advantage of ensuring that the

PFD reference clock has a 50/50 mark-space ratio. This ratio

gives the maximum separation between the fast lock timer

clock, which is generated off the falling edge of the PFD

reference, and the rising edge, which is the active edge in the

PFD. It is recommended that this toggle flip-flop be enabled for

all even R divide values greater than 2. It must be enabled if

dividing down a REFIN frequency that is greater than 120 MHz.

An optional doubler before the 4-bit R counter can be used for

low REFIN frequencies, up to 20 MHz. With these programmable

options, reference division ratios from 0.5 to 30 between REFIN

and the PFD are possible.

RF INPUT STAGE

The RF input stage is shown in Figure 21. It is followed by a

2-stage limiting amplifier to generate the CML clock levels

needed for the prescaler. Two prescaler options are selectable: a

4/5 and an 8/9. The 8/9 prescaler is selected for N divider values

greater than 80.

05328-017

BIAS

GENERATOR

1.6V

AGND

AVDD

500

500

RFIN–

RFIN+

Figure 21. RF Input Stage

RF N Divider

The RF N divider allows a fractional division ratio in the PLL

feedback path. The integer and fractional parts of the division

are programmed using separate registers, as shown in Figure 22

and described in the INT, FRAC, and MOD Relationship

section. Integer division ratios from 26 to 255 are allowed and a

third-order, Σ-Δ modulator interpolates the fractional value

between the integer steps.

05328-

018

THIRD-ORDER

FRACTIONAL

INTERPOLATOR

FRAC

VALUE

MOD

REG

INT

REG

RF N DIVIDER

N = INT + FRAC/MOD

FROM RF

INPUT STAGE

TO PFD

N COUNTER

Figure 22. Fractional-N Divider

INT, FRAC, and MOD Relationship

The INT, FRAC, and MOD values, programmed through the

serial interface, make it possible to generate RF output frequencies

that are spaced by fractions of the PFD reference frequency.

The N divider value, shown inside the brackets of the following

equation for the RF VCO frequency (RFOUT), is made up of an

integer part (INT) and a fractional part (FRAC/MOD):

RFOUT = FPFD × [INT + (FRAC/MOD)]

where:

RFOUT is the output frequency of the external VCO.

FPFD is the PFD reference frequency.

相关PDF资料 |

PDF描述 |

|---|---|

| RMC06DRTH-S734 | CONN EDGECARD 12POS DIP .100 SLD |

| HBM18DSUN | CONN EDGECARD 36POS .156 DIP SLD |

| RSC06DREI-S734 | CONN EDGECARD 12POS .100 EYELET |

| EBA24DRMI | CONN EDGECARD 48POS .125 SQ WW |

| MAX8663ETL+T | IC PMIC LI+ SNGL CELL 40TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADF4206-7EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR DUAL RF PLL FREQUENCY SYNTHESIZERS 制造商:Analog Devices 功能描述:DUAL RF PLL FREQ SYNTHESIZERS - Bulk |

| EVAL-ADF4208EB1 | 制造商:Analog Devices 功能描述:Evaluation Board For Dual RF PLL Frequency Synthesizers 制造商:Analog Devices 功能描述:DUAL RF PLL FREQ SYNTHESIZERS - Bulk |

| EVAL-ADF4212EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

| EVAL-ADF4213EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

| EVAL-ADF4213EB2 | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。