- 您现在的位置:买卖IC网 > PDF目录16560 > EVAL-ADF4193EBZ2 (Analog Devices Inc)BOARD EVALUATION EB2 FOR ADF4193 PDF资料下载

参数资料

| 型号: | EVAL-ADF4193EBZ2 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/32页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION EB2 FOR ADF4193 |

| 标准包装: | 1 |

| 主要目的: | 计时,频率合成器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ADF4193 |

| 主要属性: | 400 MHz ~ 3.5 GHz,数字式可编程输出相位 |

| 次要属性: | 板不包括环路滤波器和 VCO |

| 已供物品: | 板,缆线,CD |

| 相关产品: | ADF4193BCPZ-ND - IC PLL FREQ SYNTHESIZER 32LFCSP ADF4193BCPZ-RL7-ND - IC PLL FREQ SYNTHESIZER 32LFCSP ADF4193BCPZ-RL-ND - IC PLL FREQ SYNTHESIZER 32LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

Data Sheet

ADF4193

Rev. F | Page 17 of 32

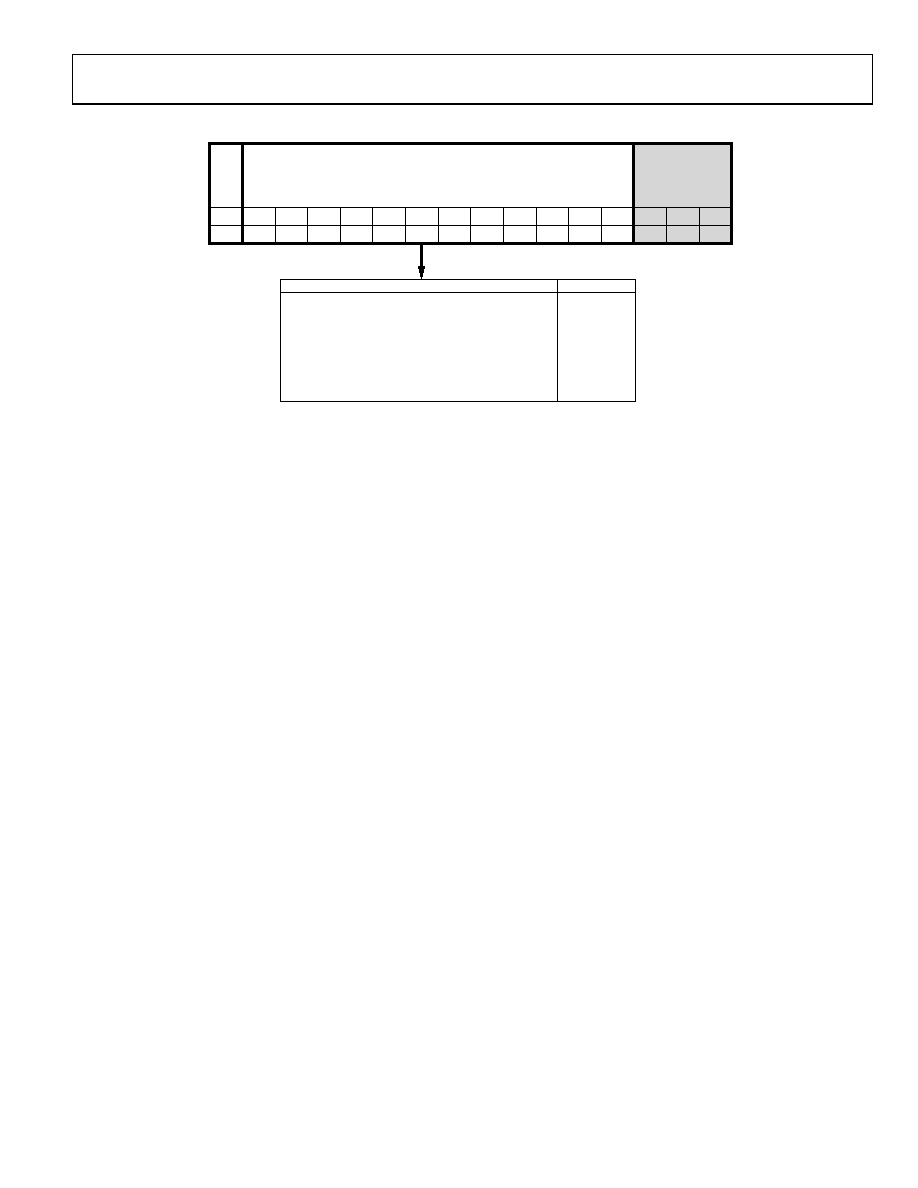

PHASE REGISTER (R2)

05328-025

DB15

0

DB14

P12

DB13

P11

DB12

P10

DB11

P9

DB10

P8

DB9

P7

DB8

P6

DB7

P5

DB6

P4

DB5

P3

DB4

P2

DB3

P1

DB2

C3 (0)

DB1

C2 (1)

DB0

C1 (0)

RESERVED

12-BIT PHASE

CONTROL

BITS

P12

0

.

1

P11

0

.

1

P10

0

.

1

..........

P3

0

.

1

P2

0

1

.

0

1

P1

0

1

0

.

0

1

0

1

PHASE VALUE1

0

1

2

.

4092

4093

4094

4095

10 = < PHASE VALUE < MOD

Figure 31. Phase Register (R2)

12-Bit Phase

The phase word sets the seed value of the Σ-Δ modulator. It can

be programmed to any integer value from 0 to MOD. As the

phase word is swept from 0 to MOD, the phase of the VCO

output sweeps over a 360° range in steps of 360°/MOD.

Note that the phase bits are double buffered. They do not take

effect until the LE of the next write to R0 (FRAC/INT register).

Therefore, if it is desired to change the phase of the VCO output

frequency, it is necessary to rewrite the INT and FRAC values to

R0, following the write to R2.

The output of a fractional-N PLL can settle to any one of the

MOD possible phase offsets with respect to the reference, where

MOD is the fractional modulus.

If it is desired to keep the output at the same phase offset with

respect to the reference, each time that particular output

frequency is programmed, then the interval between writes to

R0 must be an integer multiple of MOD reference cycles.

If it is desired to keep the outputs of two ADF4193-based

synthesizers phase coherent with each other, but not necessarily

with their common reference, then it is only required to ensure

that the write to R0 on both chips is performed during the same

reference cycle. The interval between R0 writes in this case does

not have to be an integer multiple of the MOD cycles.

Reserved Bit

The reserved bit, Bit DB15, should be set to 0.

相关PDF资料 |

PDF描述 |

|---|---|

| RMC06DRTH-S734 | CONN EDGECARD 12POS DIP .100 SLD |

| HBM18DSUN | CONN EDGECARD 36POS .156 DIP SLD |

| RSC06DREI-S734 | CONN EDGECARD 12POS .100 EYELET |

| EBA24DRMI | CONN EDGECARD 48POS .125 SQ WW |

| MAX8663ETL+T | IC PMIC LI+ SNGL CELL 40TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADF4206-7EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR DUAL RF PLL FREQUENCY SYNTHESIZERS 制造商:Analog Devices 功能描述:DUAL RF PLL FREQ SYNTHESIZERS - Bulk |

| EVAL-ADF4208EB1 | 制造商:Analog Devices 功能描述:Evaluation Board For Dual RF PLL Frequency Synthesizers 制造商:Analog Devices 功能描述:DUAL RF PLL FREQ SYNTHESIZERS - Bulk |

| EVAL-ADF4212EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

| EVAL-ADF4213EB1 | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

| EVAL-ADF4213EB2 | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。