- 您现在的位置:买卖IC网 > PDF目录223866 > GS8342TT06BGD-500T (GSI TECHNOLOGY) 4M X 8 DDR SRAM, 0.45 ns, PBGA165 PDF资料下载

参数资料

| 型号: | GS8342TT06BGD-500T |

| 厂商: | GSI TECHNOLOGY |

| 元件分类: | SRAM |

| 英文描述: | 4M X 8 DDR SRAM, 0.45 ns, PBGA165 |

| 封装: | 13 X 15 MM, 1 MM PITCH, ROHS COMPLIANT, FPBGA-165 |

| 文件页数: | 6/30页 |

| 文件大小: | 267K |

| 代理商: | GS8342TT06BGD-500T |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.00 5/2011

14/30

2011, GSI Technology

Preliminary

GS8342TT06/11/20/38BD-550/500/450/400/350

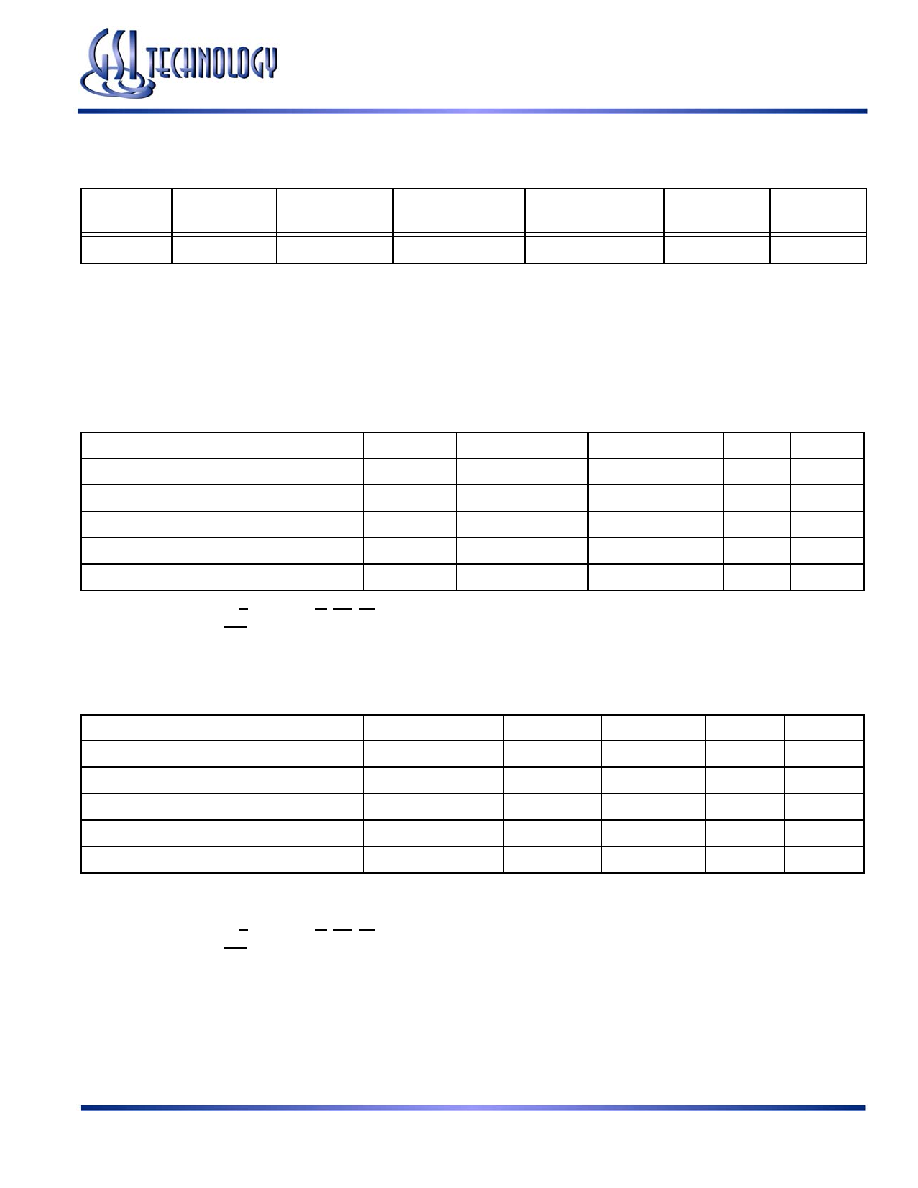

Thermal Impedance

Package

Test PCB

Substrate

JA (C°/W)

Airflow = 0 m/s

JA (C°/W)

Airflow = 1 m/s

JA (C°/W)

Airflow = 2 m/s

JB (C°/W)

JC (C°/W)

165 BGA

4-layer

TBD

Notes:

1. Thermal Impedance data is based on a number of of samples from mulitple lots and should be viewed as a typical number.

2. Please refer to JEDEC standard JESD51-6.

3. The characteristics of the test fixture PCB influence reported thermal characteristics of the device. Be advised that a good thermal path to

the PCB can result in cooling or heating of the RAM depending on PCB temperature.

HSTL I/O DC Input Characteristics

Parameter

Symbol

Min

Max

Units

Notes

Input Reference Voltage

VREF

VDDQ /2 – 0.05

VDDQ /2 + 0.05

V—

Input High Voltage

VIH1

VREF + 0.1

VDDQ + 0.3

V1

Input Low Voltage

VIL1

–0.3

VREF – 0.1

V1

Input High Voltage

VIH2

0.7 * VDDQ

VDDQ + 0.3

V2,3

Input Low Voltage

VIL2

–0.3

0.3 * VDDQ

V2,3

Notes:

1. Parameters apply to K, K, SA, DQ, R/W, BW, LD during normal operation and JTAG boundary scan testing.

2. Parameters apply to Doff, ODT during normal operation and JTAG boundary scan testing.

3. Parameters apply to ZQ during JTAG boundary scan testing only.

HSTL I/O AC Input Characteristics

Parameter

Symbol

Min

Max

Units

Notes

Input Reference Voltage

VREF

VDDQ /2 – 0.08

VDDQ /2 + 0.08

V—

Input High Voltage

VIH1

VREF + 0.2

VDDQ + 0.5

V1,2,3

Input Low Voltage

VIL1

–0.5

VREF – 0.2

V1,2,3

Input High Voltage

VIH2

VDDQ – 0.2

VDDQ + 0.5

V4,5

Input Low Voltage

VIL2

–0.5

0.2

V

4,5

Notes:

1. VIH(MAX) and VIL(MIN) apply for pulse widths less than one-quarter of the cycle time.

2. Input rise and fall times myust be a minimum of 1 V/ns, and within 10% of each other.

3. Parameters apply to K, K, SA, DQ, R/W, BW, LD during normal operation and JTAG boundary scan testing.

4. Parameters apply to Doff, ODT during normal operation and JTAG boundary scan testing.

5. Parameters apply to ZQ during JTAG boundary scan testing only.

相关PDF资料 |

PDF描述 |

|---|---|

| GS841Z36CGT-166IT | 128K X 36 ZBT SRAM, 7 ns, PQFP100 |

| GS842Z18CB-250T | 256K X 18 ZBT SRAM, 5.5 ns, PBGA119 |

| GS8641ZV18GE-200 | 4M X 18 ZBT SRAM, 7.5 ns, PBGA165 |

| GS8644Z18GE-225T | 4M X 18 ZBT SRAM, 6.5 ns, PBGA165 |

| GS8662QT10BD-200I | 8M X 9 QDR SRAM, 0.45 ns, PBGA165 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GS8342TT11BD-500 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

| GS8342TT11BD-500I | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

| GS8342TT11BD-550 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

| GS8342TT11BD-550I | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

| GS8342TT20BD-500 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

发布紧急采购,3分钟左右您将得到回复。