- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3824A (Intersil Corporation) Direct Sequence Spread Spectrum Baseband Processor PDF资料下载

参数资料

| 型号: | HFA3824A |

| 厂商: | Intersil Corporation |

| 元件分类: | 基带处理器 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | 直接序列扩频基带处理器 |

| 文件页数: | 31/40页 |

| 文件大小: | 271K |

| 代理商: | HFA3824A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

2-129

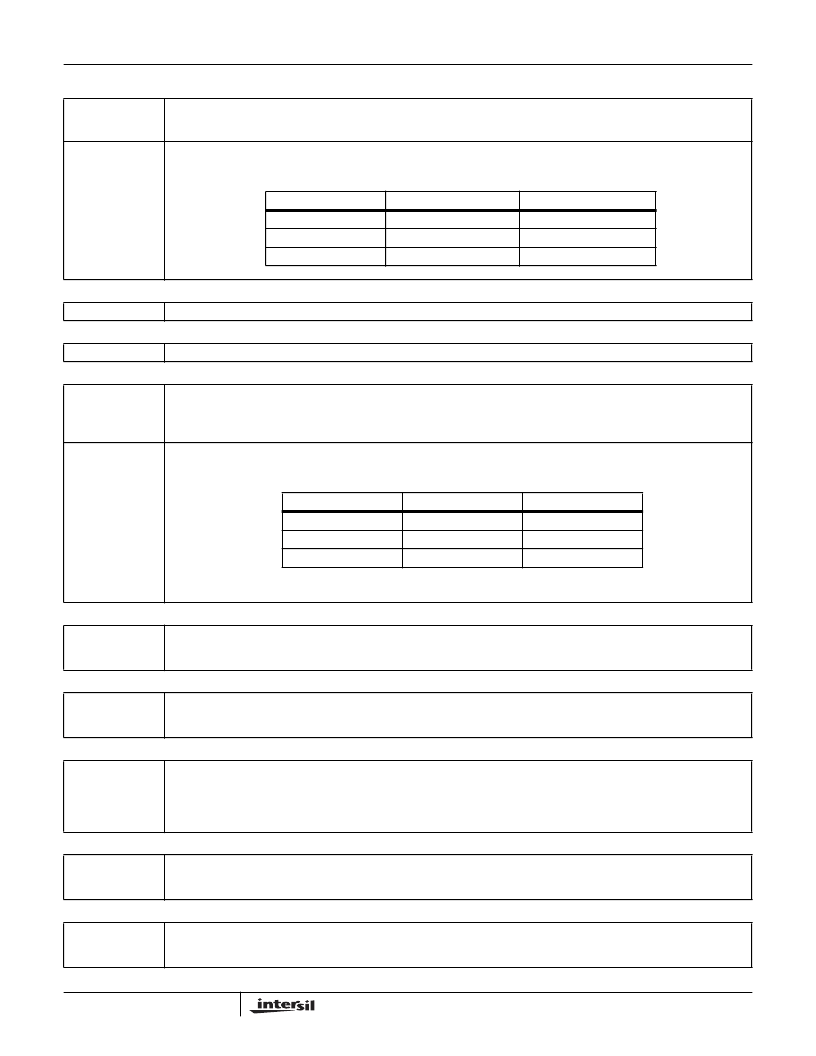

CONFIGURATION REGISTER 16 ADDRESS (40h) SCRAMBLER TAP

Bit 7

Invert the transmit Q output.

0 = Normal

1 = Invert

This register is used to configure the transmit and receiver’s scrambler with a 7-bit polynomial tap configuration. The scrambler

is a 7-bit shift register, with 7 configurable taps. A logic 1 is the respective bit position enables that particular tap. The example

below illustrates the register configuration for the polynomial F(x) = 1 + X

-4

+X

-7

. Each clock is a shift left.

Bits 0 - 6

LSB

Bits (0:6)

6 5 4 3 2 1 0

Z

-7

Z

-6

Z

-5

Z

-4

Z

-3

Z

-2

Z

-1

Scrambler Taps

F(x) = 1 + X

-4

+X

-7

1 0 0 1 0 0 0

CONFIGURATION REGISTER 17 ADDRESS (44h) RESERVED

Bits 0 - 7

Unassigned, can be set to any value.

CONFIGURATION REGISTER 18 ADDRESS (48h) RESERVED

Bits 0 - 7

Unassigned, can be set to any value.

CONFIGURATION REGISTER 19 ADDRESS (4Ch) RSSI THRESHOLD, ENERGY DETECT

Bit 7

Disable RSSI Converter, when the RSSI function is not needed, the 6 bit A/D converter can be powered down to reduce

operating current.

Logic 1 = Disable converter

Logic 0 = Enable converter

Bits 0 - 6

This register contains the value for the RSSI threshold for measuring and generating energy detect (ED). When the RSSI

exceeds the threshold ED is declared. ED indicates the presence of energy in the channel. The threshold that activates ED

is programmable. Bit 6 of this register is not used and set to Logic 0.

To disable the ED signal so that it has no affect on the CCA logic, the threshold must be set to a 3Fh (all ones). Even if bit

7 is a 1.

MSB

LSB

Bits (0:5)

5 4 3 2 1 0

0 0 0 0 0 0

00h (Min)

RSSI_STAT

1 1 1 1 1 1

3Fh (Max)

CONFIGURATION REGISTER 20 ADDRESS (50h) RX SPREAD SEQUENCE (HIGH)

Bits 0 - 7

This 8-bit register is programmed with the upper byte of the receive despreading code. This code is used for both the I and

Q signalling paths of the receiver. This register combined with the lower byte RX_SPRED(LOW) generates a receive de-

spreading code programmable up to 16 bits. Right justified MSB first. See address 13 and 14 for example.

CONFIGURATION REGISTER 21 ADDRESS (54h) RX SPREAD SEQUENCE (LOW)

Bits 0 - 7

This 8-bit register is programmed with the lower byte of the receiver despreading code. This code is used for both the I and

Q signalling paths of the receiver. This register combined with the upper byte RX_SPRED(HIGH) generates a receive de-

spreading code programmable up to 16 bits.

CONFIGURATION REGISTER 22 ADDRESS (58h) RX SIGNAL QUALITY 1 ACQ (HIGH) THRESHOLD

Bits 0 - 7

This control register contains the upper byte bits (8 - 14) of the bit sync amplitude signal quality threshold used for acquisition.

This register combined with the lower byte represents a 15-bit threshold value for the bit sync amplitude signal quality mea-

surements made during acquisition at each antenna dwell. This threshold comparison is added with the SQ2 threshold in

registers 30 and 31 for acquisition. A lower value on this threshold will increase the probability of detection and the probability

of false alarm. Set the threshold according to instructions in the text.

CONFIGURATION REGISTER 23 ADDRESS (5Ch) RX SIGNAL QUALITY 1 ACQ THRESHOLD (LOW)

Bits 0 - 7

This control register contains the lower byte bits (0 - 7) of the bit sync amplitude signal quality threshold used for acquisition.

This register combined with the upper byte represents a 15-bit threshold value for the bit sync amplitude signal quality mea-

surement made during acquisition at each antenna dwell.

CONFIGURATION REGISTER 24 ADDRESS (60h) RX SIGNAL QUALITY 1 ACQ READ (HIGH)

Bits 0 - 7

This status register contains the upper byte bits (8 - 14) of the measured signal quality threshold for the bit sync amplitude

used for acquisition. This register combined with the lower byte represents a 15-bit value, representing the measured bit

sync amplitude. This measurement is made at each antenna dwell and is the result of the best antenna.

HFA3824A

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3842B | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842BIN | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842BIN-TK | PCMCIA/USB Wireless LAN Medium Access Controller |

| HFA3842IN96 | Wireless LAN Medium Access Controller |

| HFA3842 | Wireless LAN Medium Access Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3824AIV | 制造商:Rochester Electronics LLC 功能描述:BASEBAND PROCESSOR - Bulk |

| HFA3824AIV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3824AIV96 | 制造商:Rochester Electronics LLC 功能描述:BASEBAND PROCESSOR - Bulk |

| HFA3824EVAL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3824IV | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。