- 您现在的位置:买卖IC网 > PDF目录67685 > ICS5342 PALETTE-DAC DSPL CTLR, PQCC68 PDF资料下载

参数资料

| 型号: | ICS5342 |

| 元件分类: | 显示控制器 |

| 英文描述: | PALETTE-DAC DSPL CTLR, PQCC68 |

| 封装: | PLASTIC, LCC-68 |

| 文件页数: | 1/36页 |

| 文件大小: | 1017K |

| 代理商: | ICS5342 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

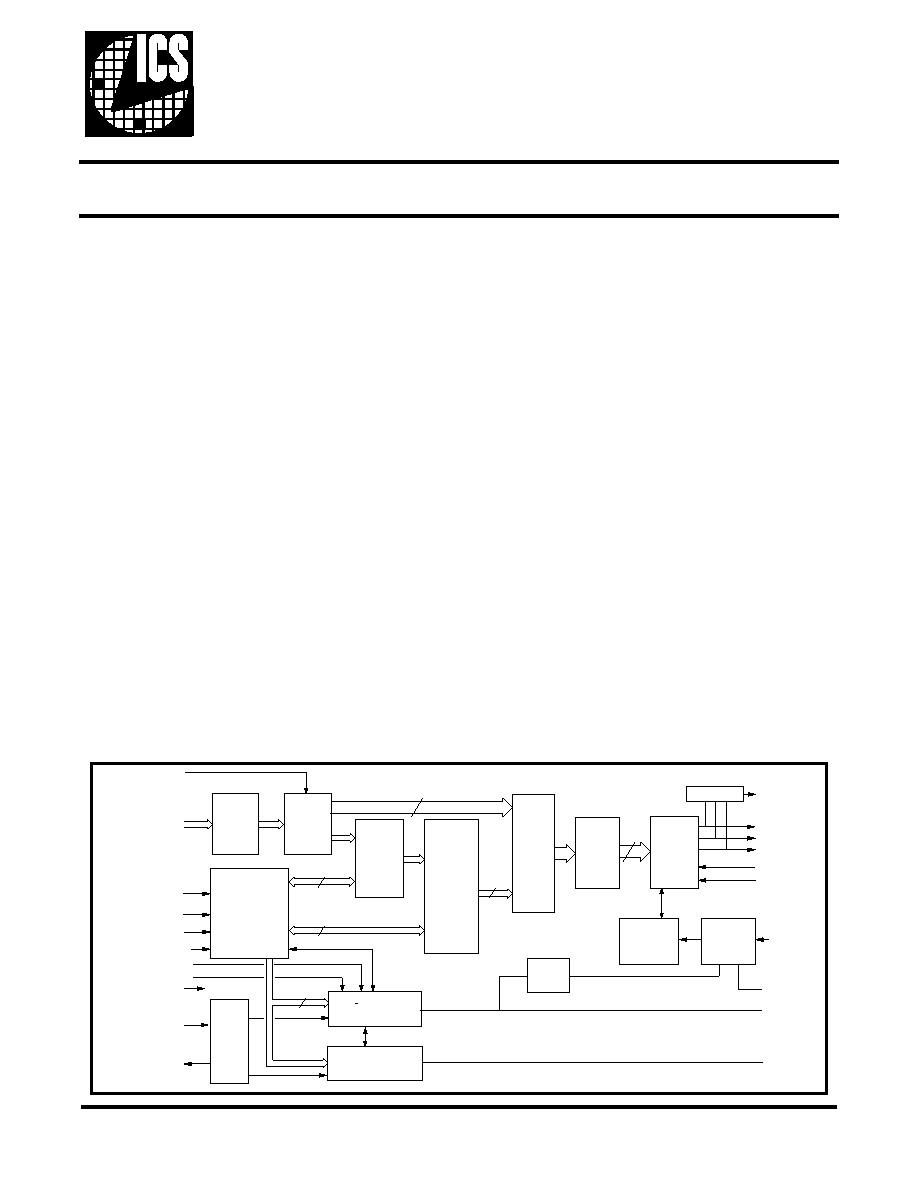

Block Schematic

PIXEL

ADR

AND

MASK

COLOR

PALETTE

256 x 18

BIT

24

18

BYPS

MUX

NORM

LATCH

24

COMPARE

TRIPLE

6/8-BIT

DAC

TIMING

GEN.

MUX.

MODE

CTL

8 PLL

PARAMETER &

CLK0 PLL

1 PLL

PARAMETER &

CLK1 PLL

2X

CLK0

CLK1

RED

GREEN

BLUE

RSET

VREF

BUFF.

LATCH

MICRO-

PROCESSOR

INTERFACE

XTAL

OSC

8

16

BLANK*

PCLK

P0-P15

D0-D7

WR*

RD*

RS0-RS2

XIN

XOUT

STROBE

CS0-CS2

PCLK

SENSE*

5342_01.ai

General Description

The ICS5342 GENDAC is a combination of dual programma-

ble clock generators, a 256 x 18-bit RAM, and a triple 8-bit

video DAC. The GENDAC supports 8-bit pseudo color appli-

cations, as well as 15-bit, 16-bit, and 24-bit True Color bypass

for high speed, direct access to the DACs.

The RAM makes it possible to display 256 colors selected

from a possible 262,144 colors. The dual clock generators use

Phase Locked Loop (PLL) technology to provide program-

mable frequencies for use in the graphics subsystem. The vid-

eo clock contains 8 frequencies, all of which are

programmable by the user. The memory clock has two pro-

grammable frequency locations.

The three 8-bit DACs on the ICS5342 are capable of driving

singly or doubly-terminated 75

loads to nominal 0 - 0.7

volts at pixel rates up to 135 MHz. Differential and integral

linearity errors are less than 1 LSB over full temperature and

VDD ranges. Monotonicity is guaranteed by design. On-chip

pixel mask register allows displayed colors to be changed in

a single write cycle rather than by modifying the color palette.

ICS is the world leader in all aspects of frequency (clock) gen-

eration for graphics, using patented techniques to produce

low jitter video timing.

Features

Triple video DAC, dual clock generator, and 16 bit pixel

port

Dynamic mode switch allows switching of color depth

on a pixel by pixel basis

24 (packed and sparse), 16, 15, or 8-bit pseudo color

pixel mode supports True Color, Hi-Color, and VGA

modes

High speed 256 x 6 x 3 color palette (135 MHz) with

bypass mode and 8-bit DACs

Eight programmable video (pixel) clock frequencies

(CLK0)

DAC power down in blanking mode

Anti-sparkle circuitry

On-chip loop lters reduce external components

Standard CPU interface

Single external crystal (typically 14.318 MHz)

Monitor sense

Internal voltage reference

135 MHz (-3), 110 MHz (-2) & 80 MHz (-1) versions

Very low clock jitter

Two latched frequency select pins or three non-latched

frequency select pins (programmable)

Hardware video checksum for manufacturing tests

ICS5342

GENDAC

16-Bit Integrated Clock-LUT-DAC

REV. 0.9.0

相关PDF资料 |

PDF描述 |

|---|---|

| ICS552ARI-01LFT | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS552R-01ILF | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS557G-05ATR | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 |

| ICS557G-08LF | 557 SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS557G-08LFT | 557 SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS5342-1 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342-2 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342-3 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342ADD | 制造商:ICS 制造商全称:ICS 功能描述:Addendum to ICS5342 Data Sheet |

| ICS5342V | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

发布紧急采购,3分钟左右您将得到回复。