- 您现在的位置:买卖IC网 > PDF目录67685 > ICS5342 PALETTE-DAC DSPL CTLR, PQCC68 PDF资料下载

参数资料

| 型号: | ICS5342 |

| 元件分类: | 显示控制器 |

| 英文描述: | PALETTE-DAC DSPL CTLR, PQCC68 |

| 封装: | PLASTIC, LCC-68 |

| 文件页数: | 31/36页 |

| 文件大小: | 1017K |

| 代理商: | ICS5342 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页

ICS5342

GENDAC

4

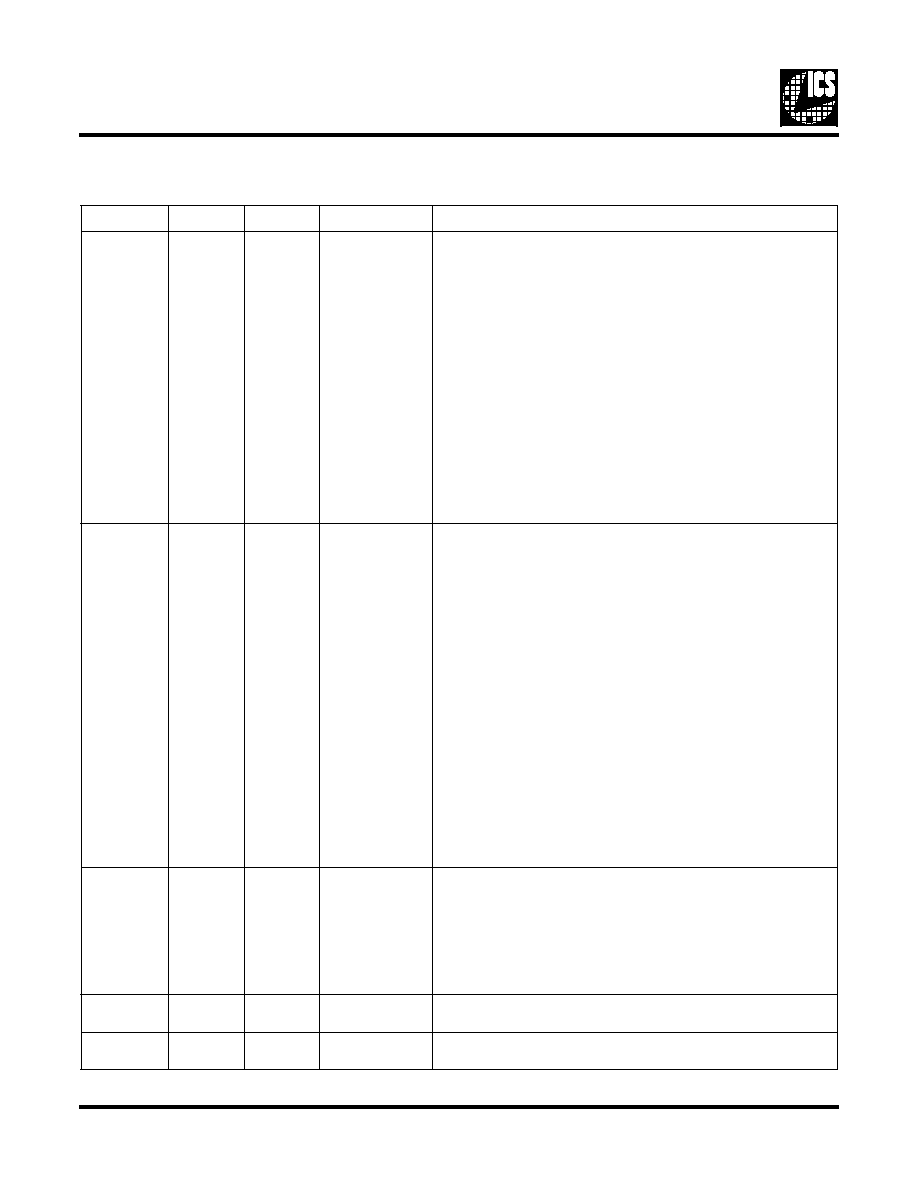

Internal Registers

RS2

RS1

RS0

Register Name

Description (all registers can be written to and read from)

The GENDAC has a single pixel address register which can be

accessed through either register address 0,0,0 or 0,1,1 – reading

from either register gives the same result.

Writing a value to address 0,0,0:

– species an address within the color palette RAM

– initializes the Color Value register

Writing a value to address 0,1,1:

– species an address within the color palette RAM

– loads Color Value register with contents of location in

addressed RAM palette and then:

– increments Pixel Address register

0

1

Pixel Address

WRITE

Writing to this 8-bit register is done before writing one or more

color values to color palette RAM.

0

1

Pixel Address

READ

Writing to this 8-bit register is done before reading one or more

color values from color palette RAM.

0

1

Color Value

The 18-bit Color Value register acts as a buffer between the

microprocessor interface and the color palette. A value may be

read from or written to this register using a three-byte transfer

sequence. The color value is contained in the least signicant 6

bits, D0-D5, of the byte read – the most signicant 2 bits are set

to zero. The same 6 bits are used when writing a byte. When

reading or writing, data is transferred in the same order – red

byte rst, then green, then blue. Each transfer between the Color

Value register and the color palette replaces the normal pixel

mapping operations of the GENDAC for a single pixel.

After writing three denitions to this register, its contents are

written to the location in the color palette RAM specied by the

Pixel Address register, before that register increments.

After reading three denitions from this register, the contents of

the location in the color palette RAM specied by the Pixel

Address registers are copied into the Color Value register, and

the Pixel Address register increments.

0

1

0

Pixel Mask

The 8-bit Pixel Mask register can be used to mask selected bits

of the Pixel Address value applied to the Pixel Address inputs

(P7-P0). A one in a position in the mask register leaves the corre-

sponding bit in the Pixel Address unaltered, while a zero sets

that bit to zero. The Pixel Mask register does not affect the Pixel

Address generated by the microprocessor interface when the pal-

ette RAM is being accessed.

1

0

PLL Address

WRITE

Writing to this 8-bit register is performed prior to writing one or

more PLL programming values to the PLL Parameter register.

1

PLL Address

READ

Writing to this 8-bit register is performed prior to reading one or

more PLL programming values from the PLL Parameter register.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS552ARI-01LFT | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS552R-01ILF | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS557G-05ATR | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 |

| ICS557G-08LF | 557 SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS557G-08LFT | 557 SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS5342-1 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342-2 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342-3 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342ADD | 制造商:ICS 制造商全称:ICS 功能描述:Addendum to ICS5342 Data Sheet |

| ICS5342V | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

发布紧急采购,3分钟左右您将得到回复。