- 您现在的位置:买卖IC网 > PDF目录67685 > ICS5342 PALETTE-DAC DSPL CTLR, PQCC68 PDF资料下载

参数资料

| 型号: | ICS5342 |

| 元件分类: | 显示控制器 |

| 英文描述: | PALETTE-DAC DSPL CTLR, PQCC68 |

| 封装: | PLASTIC, LCC-68 |

| 文件页数: | 11/36页 |

| 文件大小: | 1017K |

| 代理商: | ICS5342 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

ICS5342

GENDAC

19

out numbers with a calculator will produce a workable

combination. Multiplying possible values of (N1+2) by

the desired ratio will indicate approximately the value of

M. This method is shown in the example below. A pro-

gram could be written to try all possible combinations of

(M+2) and (N1+2) (3937 possible combinations). Dis-

card those outside the error band, and select from those

remaining by giving preference to ratios which use lower

values of (M+2). Lower values of (M+2) and (N1+2)

provide better noise rejection in the phase locked loop.

Example: Suppose you have a 14.318 MHz reference crystal

and want an output frequency of 66 MHz. You want to limit

the VCO frequency to 240 Mhz and have an error of no great-

er than 0.5%. What are the values of the PLL data registers?

A. 66*8 = 528 > 250 — VCO speed too high

66*4 = 264 > 250 — VCO speed too high

66*2 = 132 < 250 — VCO speed OK, N2 = 2, N2 code =

01 from the Post Divide Code table in the PLL Data

Registers section.

B. 132/14.31818 = 9.219 This is the desired frequency mul-

tiplication ratio.

C. Setting (N1+2) = 3,4, ...12, 13 and performing some

simple calculations yields the following table: (Note that

N1 cannot be 0).

The ratio 83/9 is closest. Thus:

(N2+2) = 9

N2=7

(M+2) = 83

M = 81

The M-byte PLL parameter word is simply 81 in binary, plus

bit 7 (which must be set to 0), or 01010001. The N-byte PLL

parameter word is N2 code (01) concatenated with 5 bits of

N2 in binary (00111), or 00100111. Once again, bit 7 must be

zero.

The combination with the least frequency error was chosen,

but several other combinations are within the 0.5% tolerance.

Because the lowest value of (M+2) offers the best damping,

the 37/4 combination will have the best power supply rejec-

tion. This results in lower jitter due to external noise.

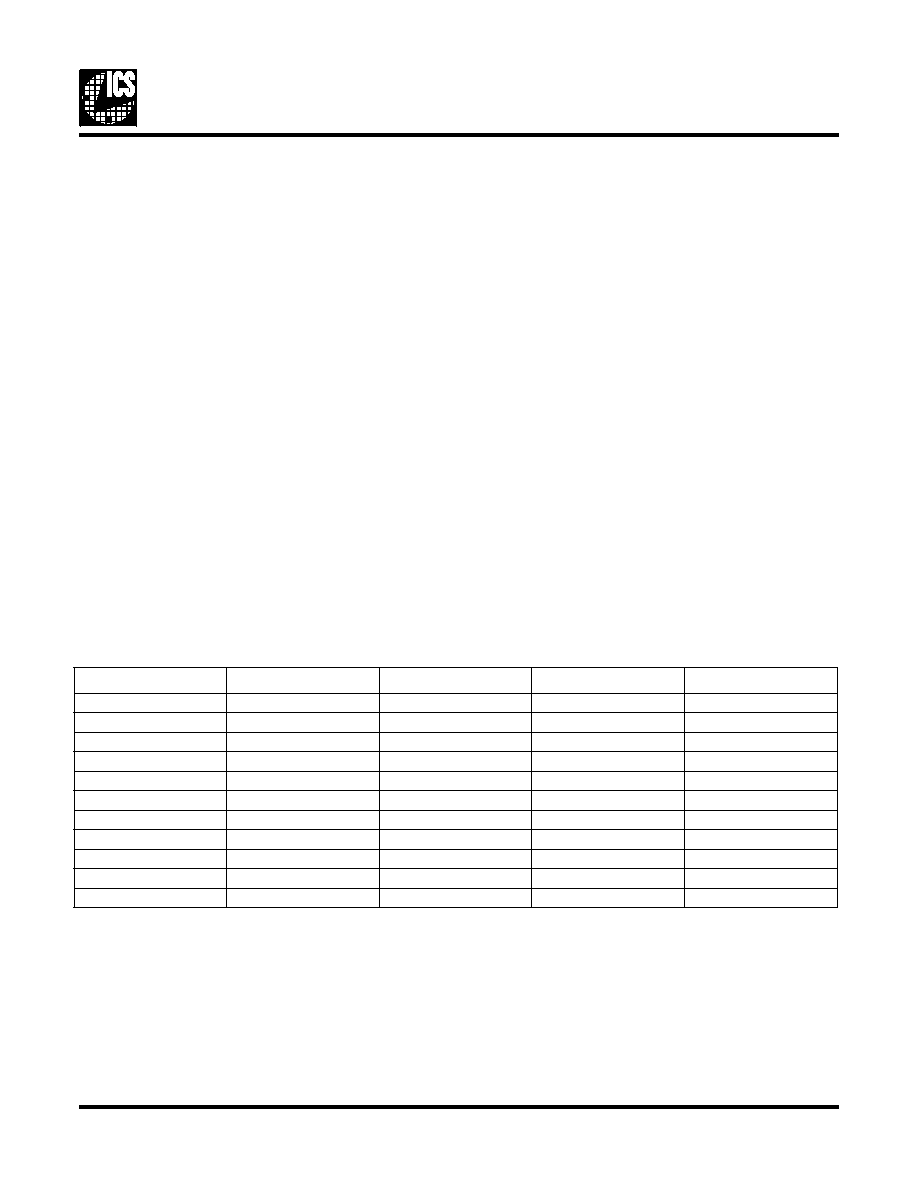

Example Calculation of PLL Data Register Values

(N1 + 2)

(N1 + 2) *9.219

rounded (=M + 2)

Actual Ratio

Percent Error

3

27.657

28

9.33

-1.23

4

36.876

37

9.25

-0.34

5

46.095

46

9.20

0.21

6

55.314

55

9.17

0.57

7

64.533

65

9.29

-0.72

8

73.752

74

9.25

-0.34

9

82.971

83

9.22

-0.03

10

92.19

92

9.20

0.21

11

101.409

101

9.18

0.40

12

110.628

111

9.25

-0.34

13

119.847

120

9.23

-0.13

相关PDF资料 |

PDF描述 |

|---|---|

| ICS552ARI-01LFT | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS552R-01ILF | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS557G-05ATR | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 |

| ICS557G-08LF | 557 SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS557G-08LFT | 557 SERIES, LOW SKEW CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS5342-1 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342-2 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342-3 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342ADD | 制造商:ICS 制造商全称:ICS 功能描述:Addendum to ICS5342 Data Sheet |

| ICS5342V | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

发布紧急采购,3分钟左右您将得到回复。