- 您现在的位置:买卖IC网 > Datasheet目录328 > IDT7026L20G (IDT, Integrated Device Technology Inc)IC SRAM 256KBIT 20NS 84PGA Datasheet资料下载

参数资料

| 型号: | IDT7026L20G |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 17/18页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 256KBIT 20NS 84PGA |

| 标准包装: | 3 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,异步 |

| 存储容量: | 256K(16K x 16) |

| 速度: | 20ns |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 84-BPGA |

| 供应商设备封装: | 84-PGA(27.94x27.94) |

| 包装: | 托盘 |

| 其它名称: | 7026L20G |

�� �

�

�

�IDT7026S/L�

�High-Speed� 16K� x� 16� Dual-Port� Static� RAM�

�Military,� Industrial� and� Commercial� Temperature� Ranges�

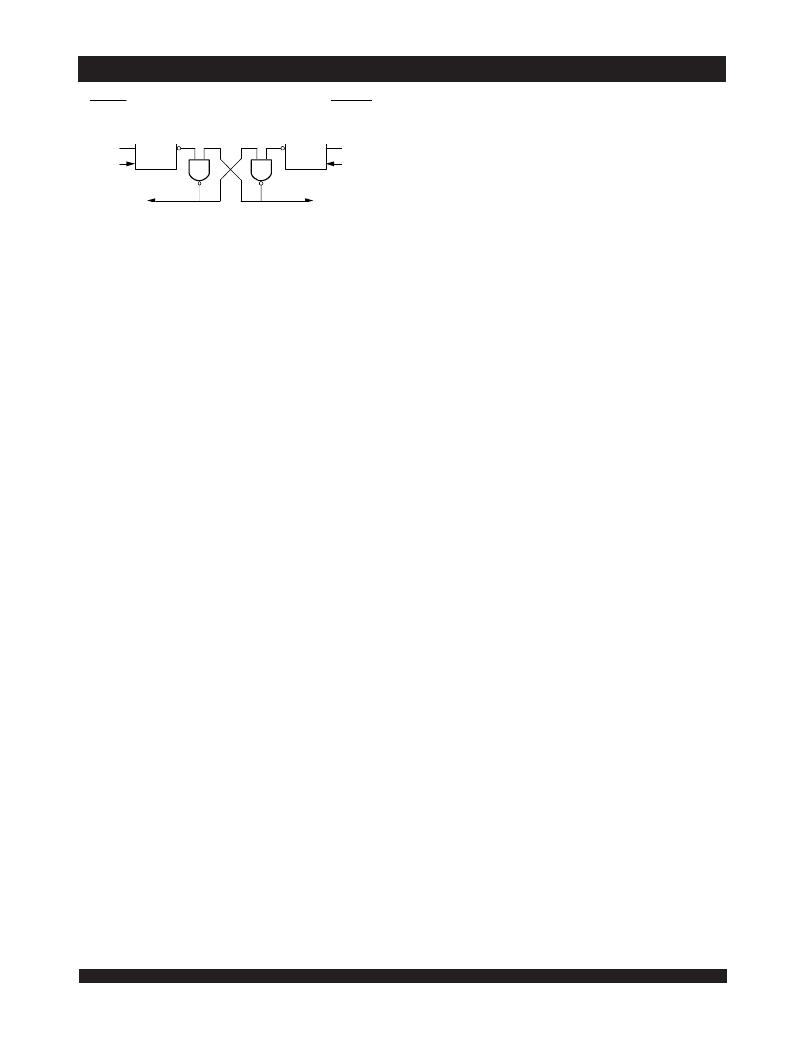

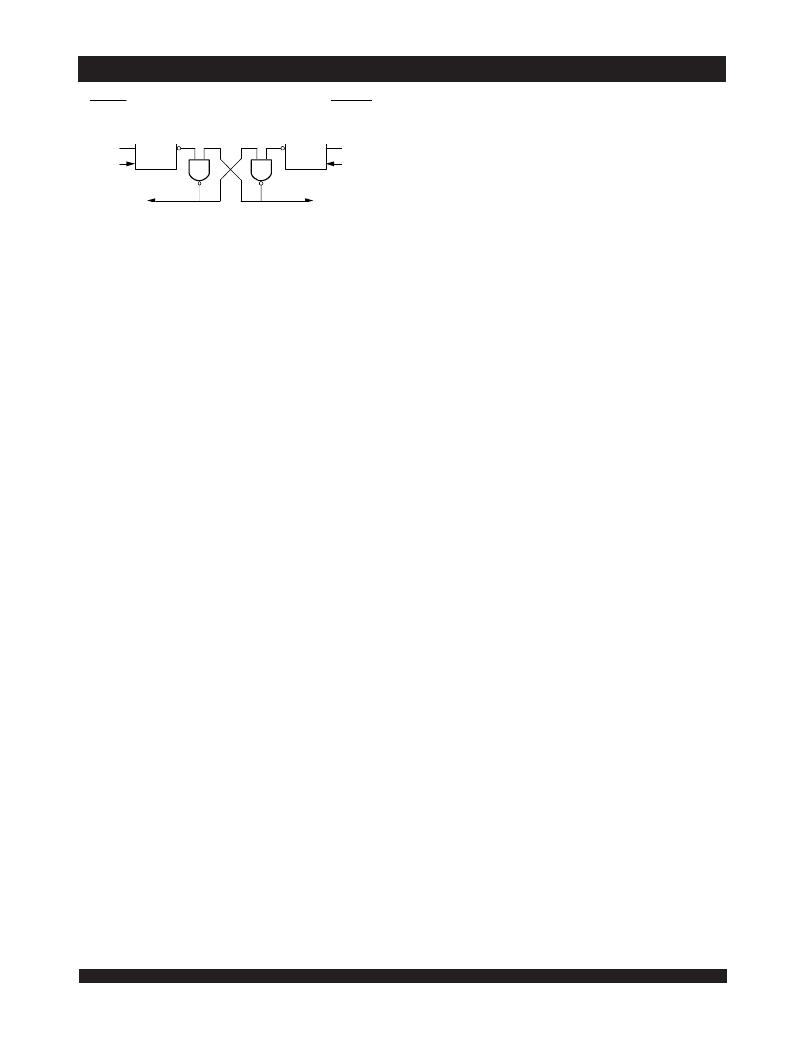

�L� PORT�

�SEMAPHORE�

�REQUEST� FLIP� FLOP�

�D� 0� D� Q�

�WRITE�

�R� PORT�

�SEMAPHORE�

�REQUEST� FLIP� FLOP�

�Q� D� D� 0�

�WRITE�

�section� by� writing,� then� reading� a� zero� into� Semaphore� 1.� If� it� succeeded�

�in� gaining� control,� it� would� lock� out� the� left� side.�

�Once� the� left� side� was� finished� with� its� task,� it� would� write� a� one� to�

�Semaphore� 0� and� may� then� try� to� gain� access� to� Semaphore� 1.� If�

�Semaphore� 1� was� still� occupied� by� the� right� side,� the� left� side� could� undo�

�its� semaphore� request� and� perform� other� tasks� until� it� was� able� to� write,� then�

�SEMAPHORE�

�READ�

�SEMAPHORE�

�READ�

�2939� drw� 17�

�Figure� 4.� IDT7026� Semaphore� Logic�

�,�

�read� a� zero� into� Semaphore� 1.� If� the� right� processor� performs� a� similar� task�

�with� Semaphore� 0,� this� protocol� would� allow� the� two� processors� to� swap�

�8K� blocks� of� Dual-Port� RAM� with� each� other.�

�The� blocks� do� not� have� to� be� any� particular� size� and� can� even� be�

�variable,� depending� upon� the� complexity� of� the� software� using� the�

�semaphore� flags.� All� eight� semaphores� could� be� used� to� divide� the� Dual-�

�semaphores� alone� do� not� guarantee� that� access� to� a� resource� is� secure.�

�As� with� any� powerful� programming� technique,� if� semaphores� are� misused�

�or� misinterpreted,� a� software� error� can� easily� happen.�

�Initialization� of� the� semaphores� is� not� automatic� and� must� be� handled�

�via� the� initialization� program� at� power-up.� Since� any� semaphore� request�

�flag� which� contains� a� zero� must� be� reset� to� a� one,� all� semaphores� on� both�

�sides� should� have� a� one� written� into� them� at� initialization� from� both� sides�

�to� assure� that� they� will� be� free� when� needed.�

�Using� Semaphores—Some� Examples�

�Perhaps� the� simplest� application� of� semaphores� is� their� application�

�as� resource� markers� for� the� IDT7026’s� Dual-Port� RAM.� Say� the� 16K� x�

�16� RAM� was� to� be� divided� into� two� 8K� x� 16� blocks� which� were� to� be�

�dedicated� at� any� one� time� to� servicing� either� the� left� or� right� port.� Semaphore�

�0� could� be� used� to� indicate� the� side� which� would� control� the� lower� section�

�of� memory,� and� Semaphore� 1� could� be� defined� as� the� indicator� for� the�

�upper� section� of� memory.�

�To� take� a� resource,� in� this� example� the� lower� 8K� of� Dual-Port� RAM,�

�the� processor� on� the� left� port� could� write� and� then� read� a� zero� in� to�

�Semaphore� 0.� If� this� task� were� successfully� completed� (a� zero� was�

�read� back� rather� than� a� one),� the� left� processor� would� assume� control�

�of� the� lower� 8K.� Meanwhile� the� right� processor� was� attempting� to� gain�

�control� of� the� resource� after� the� left� processor,� it� would� read� back� a� one�

�in� response� to� the� zero� it� had� attempted� to� write� into� Semaphore� 0.� At� this�

�Port� RAM� or� other� shared� resources� into� eight� parts.� Semaphores� can�

�even� be� assigned� different� meanings� on� different� sides� rather� than� being�

�given� a� common� meaning� as� was� shown� in� the� example� above.�

�Semaphores� are� a� useful� form� of� arbitration� in� systems� like� disk�

�interfaces� where� the� CPU� must� be� locked� out� of� a� section� of� memory� during�

�a� transfer� and� the� I/O� device� cannot� tolerate� any� wait� states.� With� the� use�

�of� semaphores,� once� the� two� devices� has� determined� which� memory� area�

�was� “off-limits”� to� the� CPU,� both� the� CPU� and� the� I/O� devices� could� access�

�their� assigned� portions� of� memory� continuously� without� any� wait� states.�

�Semaphores� are� also� useful� in� applications� where� no� memory� “WAIT”�

�state� is� available� on� one� or� both� sides.� Once� a� semaphore� handshake� has�

�been� performed,� both� processors� can� access� their� assigned� RAM�

�segments� at� full� speed.�

�Another� application� is� in� the� area� of� complex� data� structures.� In� this�

�case,� block� arbitration� is� very� important.� For� this� application� one� processor�

�may� be� responsible� for� building� and� updating� a� data� structure.� The� other�

�processor� then� reads� and� interprets� that� data� structure.� If� the� interpreting�

�processor� reads� an� incomplete� data� structure,� a� major� error� condition� may�

�exist.� Therefore,� some� sort� of� arbitration� must� be� used� between� the� two�

�different� processors.� The� building� processor� arbitrates� for� the� block,� locks�

�it� and� then� is� able� to� go� in� and� update� the� data� structure.� When� the� update�

�is� completed,� the� data� structure� block� is� released.� This� allows� the�

�interpreting� processor� to� come� back� and� read� the� complete� data� structure,�

�thereby� guaranteeing� a� consistent� data� structure.�

�point,� the� software� could� choose� to� try� and� gain� control� of� the� second� 8K�

�17�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT7027L25G | IC SRAM 512KBIT 25NS 108PGA |

| IDT7028L20PFI | IC SRAM 1MBIT 20NS 100TQFP |

| IDT7034L20PFI | IC SRAM 72KBIT 20NS 100TQFP |

| IDT7035L20PFI | IC SRAM 144KBIT 20NS 100TQFP |

| IDT7037L20PFI | IC SRAM 576KBIT 20NS 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT7026L20J | 功能描述:IC SRAM 256KBIT 20NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT7026L20J8 | 功能描述:IC SRAM 256KBIT 20NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT7026L20JI | 功能描述:IC SRAM 256KBIT 20NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT7026L20JI8 | 功能描述:IC SRAM 256KBIT 20NS 84PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT7026L25G | 功能描述:IC SRAM 256KBIT 25NS 84PGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。