- 您现在的位置:买卖IC网 > PDF目录1924 > IDT82V2042EPFG (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 2CH SHORT 80TQFP PDF资料下载

参数资料

| 型号: | IDT82V2042EPFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 10/83页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 2CH SHORT 80TQFP |

| 标准包装: | 45 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 82V2042EPFG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

IDT82V2042E

DUAL CHANNEL T1/E1/J1 SHORT HAUL LINE INTERFACE UNIT

FUNCTIONAL DESCRIPTION

18

December 12, 2005

3

FUNCTIONAL DESCRIPTION

3.1

CONTROL MODE SELECTION

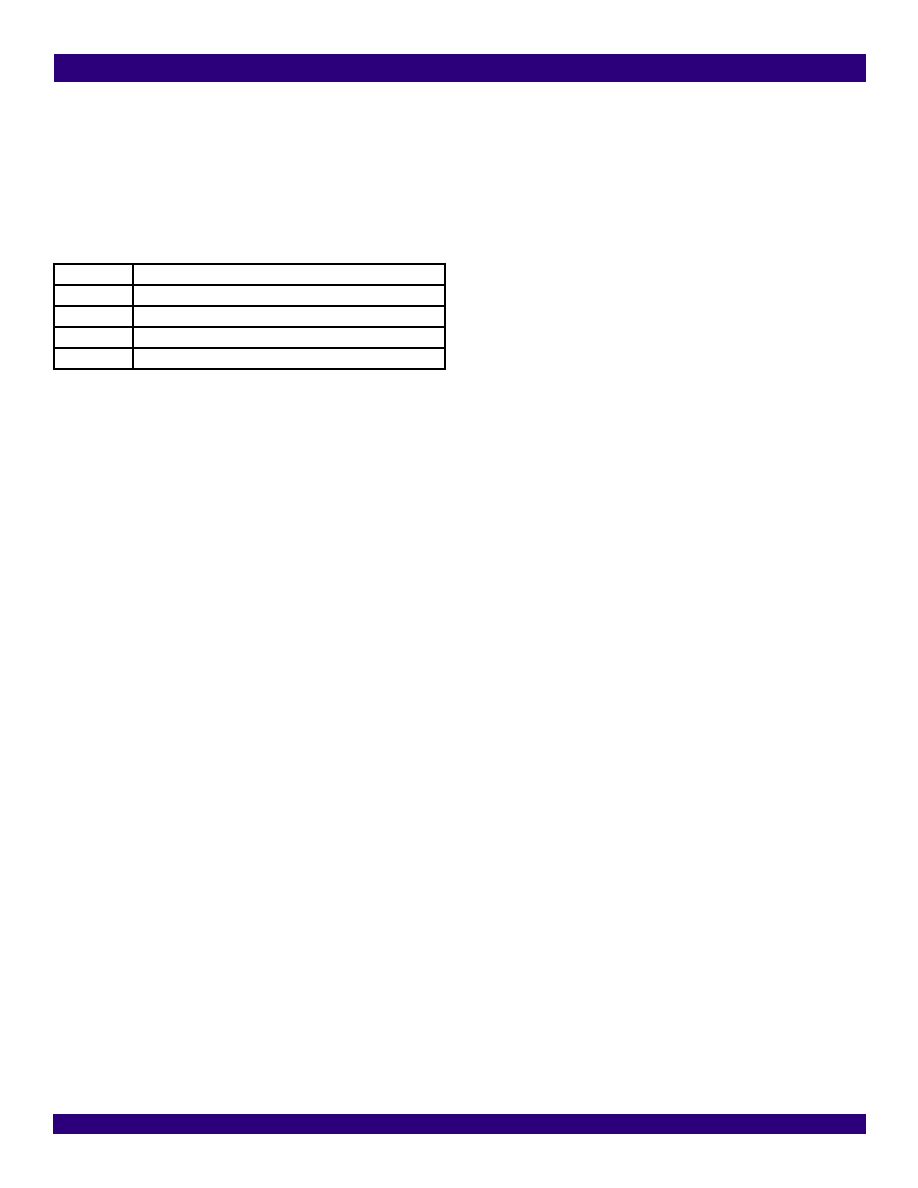

The IDT82V2042E can be configured by software or by hardware. The

softwarecontrolmodesupportsSerialControlInterface,Motorolanon-Mul-

tiplexed Control Interface and Intel non-Multiplexed Control Interface. The

Control mode is selected by MODE1 and MODE0 pins as follows:

The serial microcontroller Interface consists of CS, SCLK, SCLKE,

SDI, SDO and INT pins. SCLKE is used for the selection of active

edge of SCLK.

The parallel non-Multiplexed microcontroller Interface consists of

CS, A[5:0], D[7:0], DS/RD, R/W/WR and INT pins.

Hardware interface consists of PULSn[3:0], THZ, RCLKE, LPn[1:0],

PATTn[1:0], JA[1:0], MONTn, TERMn, RPDn, MODE[1:0] and

RXTXM[1:0] (n=1, 2). Refer to 5 HARDWARE CONTROL PIN SUM-

for details about hardware control.

3.2

T1/E1/J1 MODE SELECTION

When the chip is configured by software, T1/E1/J1 mode is selected by

the T1E1 bit (GCF, 20H). In E1 application, the T1E1 bit (GCF, 20H) should

be set to ‘0’. In T1/J1 application, the T1E1 bit should be set to ‘1’.

When the chip is configured by hardware, T1/E1/J1 mode is selected

by PULSn[3:0] pins on a per channel basis. These pins also determine

transmit pulse template and internal termination impedance. Refer to 5

for details.

3.3

TRANSMIT PATH

The transmit path of each channel of IDT82V2042E consists of an

Encoder, an optional Jitter Attenuator, a Waveform Shaper, a Line Driver

and a Programmable Transmit Termination.

3.3.1

TRANSMIT PATH SYSTEM INTERFACE

The transmit path system interface consists of TCLKn pin, TDn/TDPn

pin and TDNn pin. In E1 mode, TCLKn is a 2.048 MHz clock. In T1/J1 mode,

TCLKn is a 1.544 MHz clock. If TCLKn is missing for more than 70 MCLK

cycles, an interrupt will be generated if it is not masked.

Transmit data is sampled on theTDn/TDPnand TDNnpins bythe active

edge of TCLKn. The active edge of TCLKn can be selected by the

TCLK_SELbit(TCF0,04H...).AndtheactivelevelofthedataonTDn/TDPn

and TDNn can be selected by the TD_INV bit (TCF0, 04H...). In hardware

control mode, the falling edge of TCLKn and the active high of transmit data

are always used.

The transmit data from the system side can be provided in two different

ways: Single Rail and Dual Rail. In Single Rail mode, only TDn pin is used

for transmitting data and the T_MD[1] bit (TCF0, 04H...) should be set to

‘0’.InDualRailMode,bothTDPnpinandTDNnpinareusedfortransmitting

data, the T_MD[1] bit (TCF0, 04H...) should be set to ‘1’.

3.3.2

ENCODER

In Single Rail mode, when T1/J1 mode is selected, the Encoder can be

selected to be a B8ZS encoder or an AMI encoder by setting T_MD[0] bit

(TCF0, 04H...).

InSingleRailmode,whenE1modeisselected,theEncodercanbecon-

figured to be a HDB3 encoder or an AMI encoder by setting T_MD[0] bit

(TCF0, 04H...).

In both T1/J1 mode and E1 mode, when Dual Rail mode is selected (bit

T_MD[1] is ‘1’), the Encoder is by-passed. In Dual Rail mode, a logic ‘1’ on

the TDPn pin and a logic ‘0’ on the TDNn pin results in a negative pulse on

the TTIPn/TRINGn; a logic ‘0’ on TDPn pin and a logic ‘1’ on TDNn pin

results in a positive pulse on the TTIPn/TRINGn. If both TDPn and TDNn

are high or low, the TTIPn/TRINGn outputs a space (Refer to TDn/TDPn,

In hardware control mode, the operation mode of receive and transmit

path can be selected by setting RXTXM1 and RXTXM0 pins on a global

basis. Refer to 5 HARDWARE CONTROL PIN SUMMARY for details.

3.3.3

PULSE SHAPER

The IDT82V2042E provides two ways of manipulating the pulse shape

before sending it. One is to use preset pulse templates; the other is to use

user-programmable arbitrary waveform template.

In software control mode, the pulse shape can be selected by setting

the related registers.

In hardware control mode, the pulse shape can be selected by setting

PULSn[3:0] pins on a per channel basis. Refer to 5 HARDWARE CONTROL

for details.

3.3.3.1 Preset Pulse Templates

For E1 applications, the pulse shape is shown in Figure-3 according to

the G.703 and the measuring diagram is shown in Figure-4. In internal

impedance matching mode, if the cable impedance is 75

, the PULS[3:0]

bits (TCF1, 05H...) should be set to ‘0000’; if the cable impedance is 120

, the PULS[3:0] bits (TCF1, 05H...) should be set to ‘0001’. In external

impedance matching mode, for both E1/75

and E1/120 cable imped-

ance, PULS[3:0] should be set to ‘0001’.

Control Interface Mode

00

Hardware interface

01

Serial Microcontroller Interface.

10

Parallel -non-Multiplexed -Motorola Interface

11

Parallel -non-Multiplexed -Intel Interface

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V2044EPFG | IC LIU T1/E1 QUAD SHORT 128-TQFP |

| IDT82V2048DAG | IC LIU T1/E1 8CH SHORT 144-TQFP |

| IDT82V2048EDR | IC LIU T1/E1 8CH SHORT 208-TQFP |

| IDT82V2048LBBG | IC LIU T1/E1 8CH SHORT 160-BGA |

| IDT82V2048SDAG | IC LIU T1/E1 8CH SHORT 144-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2042EPFG8 | 功能描述:IC LIU T1/J1/E1 2CH SHORT 80TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2044 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD T1/E1 SHORT HAUL LINE INTERFACE UNIT |

| IDT82V2044BB | 功能描述:IC LIU T1/E1 QUAD SHORT 160-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2044BBG | 功能描述:IC LIU T1/E1 QUAD SHORT 160-BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2044DA | 功能描述:IC LIU T1/E1 QUAD SHORT 144-TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。