- 您现在的位置:买卖IC网 > PDF目录1924 > IDT82V2042EPFG (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 2CH SHORT 80TQFP PDF资料下载

参数资料

| 型号: | IDT82V2042EPFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 28/83页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 2CH SHORT 80TQFP |

| 标准包装: | 45 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 82V2042EPFG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

IDT82V2042E

DUAL CHANNEL T1/E1/J1 SHORT HAUL LINE INTERFACE UNIT

FUNCTIONAL DESCRIPTION

34

December 12, 2005

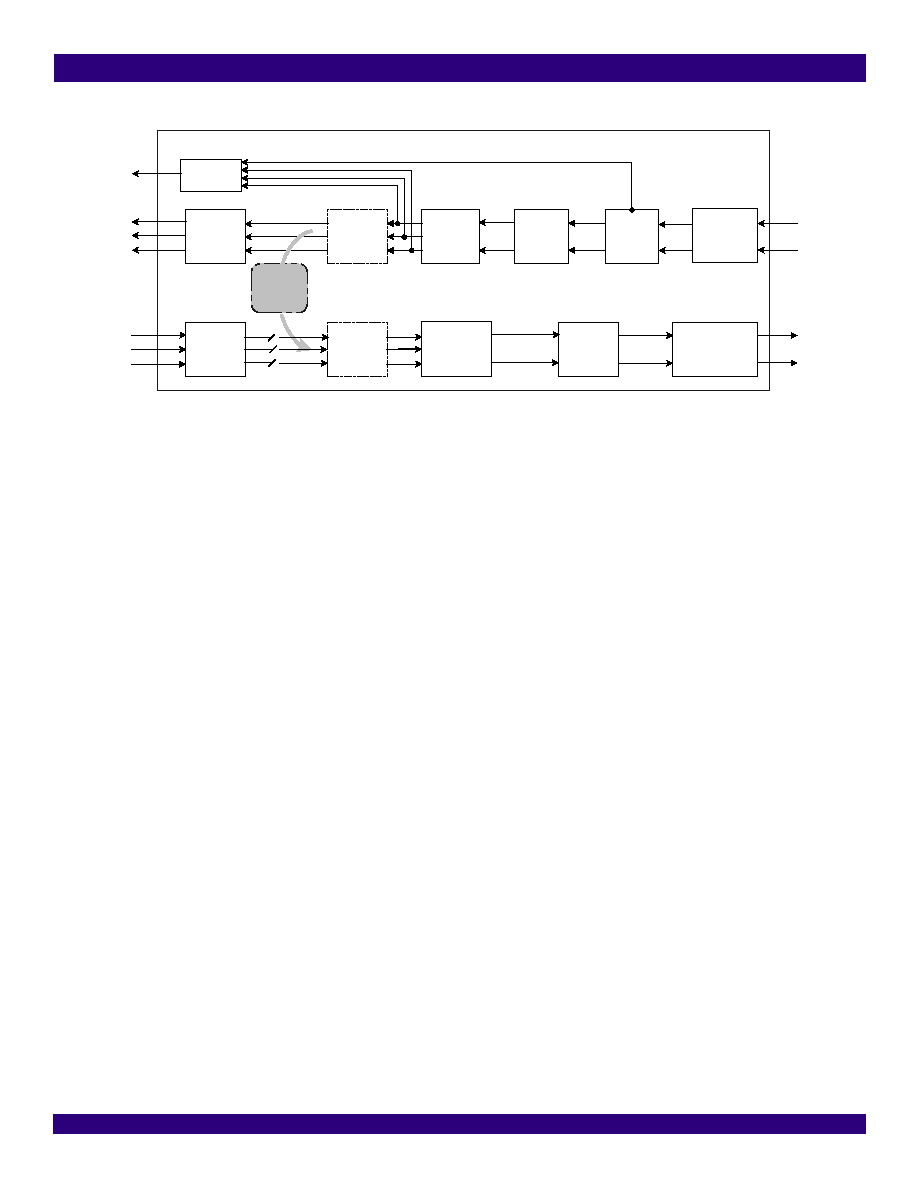

Figure-16 Remote Loopback

3.8.4

INBAND LOOPBACK

When PATT[1:0] bits (MAINT0, 0CH...) are set to ‘11’, the correspond-

ing channel is configured in Inband Loopback mode. In this mode, an

unframed activate/Deactivate Loopback Code is generated repeatedly in

transmit direction per ANSI T1. 403 which overwrite the transmit signals.

In receive direction, the framed or unframed code is detected per ANSI T1.

403, even in the presence of 10-2 bit error rate.

If the Automatic Remote Loopback is enabled by setting ARLP bit

(MAINT1, 0DH...) to ‘1’, the chip will establish/demolish the Remote Loop-

back based on the reception of the Activate Loopback Code/ Deactivate

Loopback Code for 5.1 s. If the ARLP bit (MAINT1, 0DH...) is set to ‘0’, the

Remote Loopback can also be demolished forcedly.

3.8.4.1 Transmit Activate/Deactivate Loopback Code

The pattern of the transmit Activate/Deactivate Loopback Code is

defined by the TIBLB[7:0] bits (MAINT3, 0FH...). Whether the code repre-

sentsanActivateLoopbackCodeoraDeactivateLoopbackCodeisjudged

by the far end receiver. The length of the pattern ranges from 5 bits to 8 bits,

as selected by the TIBLB_L[1:0] bits (MAINT2, 0EH...). The pattern can be

programmed to 6-bit-long or 8-bit-long respectively by repeating itself if it

is 3-bit-long or 4-bit-long. When the PATT[1:0] bits (MAINT0, 0CH...) are

set to ‘11’, the transmission of the Activate/Deactivate Loopback Code is

initiated. If the PATT_CLK bit (MAINT0, 0CH...) is set to ‘0’ and the

PATT[1:0]bits(MAINT0,0CH...)areset to‘00’,thetransmissionofthe Acti-

vate/Deactivate Loopback Code will stop.

The local transmit activate/deactivate code setting should be the same

as the receive code setting in the remote end. It is the same thing for the

other way round.

3.8.4.2 Receive Activate/Deactivate Loopback Code

The pattern of the receive Activate Loopback Code is defined by the

RIBLBA[7:0] bits (MAINT4, 10H...). The length of this pattern ranges from

5 bits to 8 bits, as selected by the RIBLBA_L [1:0] bits (MAINT2, 0EH...).

The pattern can be programmed to 6-bit-long or 8-bit-long respectively by

repeating itself if it is 3-bit-long or 4-bit-long.

The pattern of the receive Deactivate Loopback Code is defined by the

RIBLBD[7:0] bits (MAINT5, 11H...). The length of the receive Deactivate

Loopback Code ranges from 5 bits to 8 bits, as selected by the

RIBLBD_L[1:0] bits (MAINT2, 0EH...). The pattern can be programmed to

6-bit-long or 8-bit-long respectively by repeating itself if it is 3-bit-long or 4-

bit-long.

After the Activate Loopback Code has been detected in the receive data

for more than 30 ms (in E1 mode) / 40 ms (in T1/J1 mode), the IBLBA_S

bit (STAT0, 16H...) will be set to ‘1’ to declare the reception of the Activate

Loopback Code.

After the Deactivate Loopback Code has been detected in the receive

dataformorethan30ms(InE1mode)/40ms(InT1/J1mode),theIBLBD_S

bit(STAT0,16H...)willbesetto‘1’todeclarethereceptionoftheDeactivate

Loopback Code.

When the IBLBA_IES bit (INTES, 15H...) is set to ‘0’, only the ‘0’ to ‘1’

transitionof theIBLBA_S bitwillgeneratean interruptandset theIBLBA_IS

bit (INTS0, 18H...) to ‘1’. When the IBLBA_IES bit is set to ‘1’, any changes

of the IBLBA_S bit will generate an interrupt and set the IBLBA_IS bit

(INTS0, 18H...) to ‘1’. The IBLBA_IS bit will be reset to ‘0’ after being read.

When the IBLBD_IES bit (INTES, 15H...) is set to ‘0’, only the ‘0’ to ‘1’

transitionoftheIBLBD_SbitwillgenerateaninterruptandsettheIBLBD_IS

bit (INTS0, 18H...) to ‘1’. When the IBLBD_IES bit is set to ‘1’, any changes

of the IBLBD_S bit will generate an interrupt and set the IBLBD_IS bit

(INTS0, 18H...) to ‘1’. The IBLBD_IS bit will be reset to ‘0’ after being read.

B8ZS/

HDB3/AMI

Encoder

Jitter

Attenuator

B8ZS/

HDB3/AMI

Decoder

Jitter

Attenuator

Data

Slicer

Adaptive

Equalizer

LOS/AIS

Detection

Clock and

Data

Recovery

Receiver

Internal

Termination

TCLKn

TDNn

TDn/TDPn

RCLKn

CVn/RDNn

LOSn

RDn/RDPn

RRINGn

TTIPn

TRINGn

RTIPn

Remote

Loopback

Line

Driver

Waveform

Shaper

Transmitter

Internal

Termination

One of the Two Identical Channels

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V2044EPFG | IC LIU T1/E1 QUAD SHORT 128-TQFP |

| IDT82V2048DAG | IC LIU T1/E1 8CH SHORT 144-TQFP |

| IDT82V2048EDR | IC LIU T1/E1 8CH SHORT 208-TQFP |

| IDT82V2048LBBG | IC LIU T1/E1 8CH SHORT 160-BGA |

| IDT82V2048SDAG | IC LIU T1/E1 8CH SHORT 144-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2042EPFG8 | 功能描述:IC LIU T1/J1/E1 2CH SHORT 80TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2044 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD T1/E1 SHORT HAUL LINE INTERFACE UNIT |

| IDT82V2044BB | 功能描述:IC LIU T1/E1 QUAD SHORT 160-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2044BBG | 功能描述:IC LIU T1/E1 QUAD SHORT 160-BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2044DA | 功能描述:IC LIU T1/E1 QUAD SHORT 144-TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。