- 您现在的位置:买卖IC网 > Datasheet目录331 > IPT-C2H-NIOS (Altera)C2H COMPILER FOR NIOS II Datasheet资料下载

参数资料

| 型号: | IPT-C2H-NIOS |

| 厂商: | Altera |

| 文件页数: | 86/138页 |

| 文件大小: | 0K |

| 描述: | C2H COMPILER FOR NIOS II |

| 标准包装: | 1 |

| 系列: | Nios®II |

| 类型: | Nios II |

| 功能: | C 到硬件编译器 |

| 许可证: | 初始许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页当前第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页

�� �

�

�

�Scheduling�

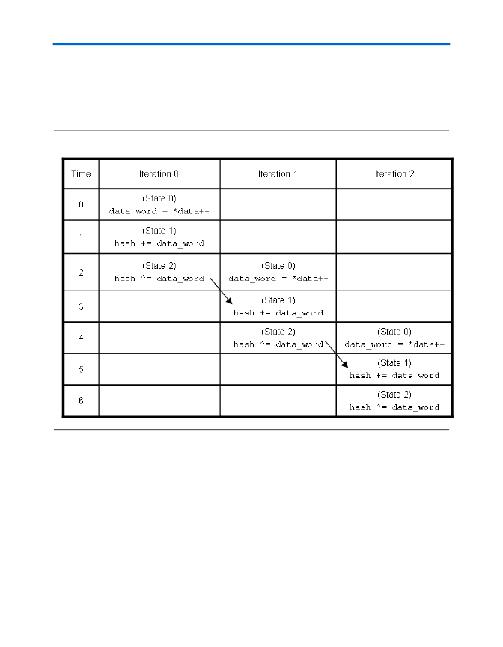

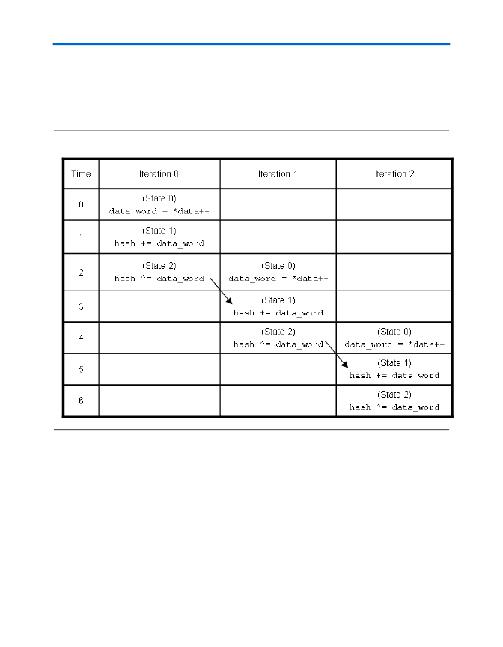

�Figure� 3–23� illustrates� how� the� C2H� Compiler� schedules� successive�

�iterations� of� the� loop� shown� in� Figure� 3–22� ,� based� on� the� restrictions�

�imposed� by� hash� .� State� 1� cannot� execute� until� the� previous� iteration� has�

�completed� State� 2.� The� C2H� Compiler� schedules� the� states� as� shown� in�

�Figure� 3–23� to� satisfy� the� loop-carried� dependency.�

�Figure� 3–23.� Pipelined� Loop� Iterations� with� a� Loop-Carried� Dependency�

�In� Figure� 3–23� ,� the� cyclic� arrow� for� hash� in� Figure� 3–22� translates� to�

�straight� arrows� between� iterations.�

�Pipelining� Avalon-MM� Read� Transfers� from� Multiple� Iterations�

�As� discussed� in� section� “Read� Operations� with� Latency”� on� page� 3–37� ,�

�the� C2H� Compiler� is� aware� of� read� latency� in� slave� memories.� Master�

�ports� on� C2H� accelerators� can� use� Avalon-MM� pipelined� read� transfers,�

�which� allow� multiple� read� transfers� to� be� pending� at� a� given� time.� As� a�

�result,� for� a� loop� that� reads� from� memory� with� latency,� the� next� iteration�

�of� the� loop� can� begin� fetching� data� before� data� from� the� previous� iteration�

�has� returned.� For� such� a� loop,� the� C2H� Compiler� creates� a� master� port�

�3–46�

�Nios� II� C2H� Compiler� User� Guide�

�9.1�

�Altera� Corporation�

�November� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| IPTR-DSPBUILDER | DSP BUILDER SOFTWARE |

| IR11662SPBF | IC CNTROL SMART RECTIFIER 8-SOIC |

| IR1166STRPBF | IC MOSFET DRIVER N-CH 200V 8SOIC |

| IR11672ASPBF | IC MOSFET DRIVER 200V 8-SOIC |

| IR1167ASTRPBF | IC SMART SECONDARY DRIVER 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPT-DSPBUILDER | 功能描述:开发软件 DSP Builder MATLAB SIMULINK RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPTE-75GF-1000-70D | 制造商: 功能描述: 制造商:undefined 功能描述: |

| IPTG06A18-11SZC | 制造商:GLENAIR 制造商全称:Glenair, Inc. 功能描述:Straight Plug Connector with Backshell to Accommodate |

| IPTG06A18-11SZCPH16 | 制造商:GLENAIR 制造商全称:Glenair, Inc. 功能描述:Straight Plug Connector |

| IPTG06A18-11SZCPHM18 | 制造商:GLENAIR 制造商全称:Glenair, Inc. 功能描述:Straight Plug Connector |

发布紧急采购,3分钟左右您将得到回复。