参数资料

| 型号: | ISL6277IRZ |

| 厂商: | Intersil |

| 文件页数: | 25/37页 |

| 文件大小: | 0K |

| 描述: | IC PWM REG MULTIPH AMD 48-QFN |

| 标准包装: | 50 |

| 应用: | 控制器,AMD Fusion? SVI 2.0 CPU GPU |

| 输入电压: | 4.5 V ~ 25 V |

| 输出数: | 2 |

| 输出电压: | 0.006 V ~ 1.55 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(6x6) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

�� �

�

�

�ISL6277�

�VID�

�VID� bits� [7:1]�

�bit� [0]�

�SVC�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�1� 4�

�15�

�16�

�17�

�18�

�19�

�20�

�21�

�22�

�23�

�24�

�25�

�26�

�27�

�SVD�

�ACK�

�ACK�

�ACK�

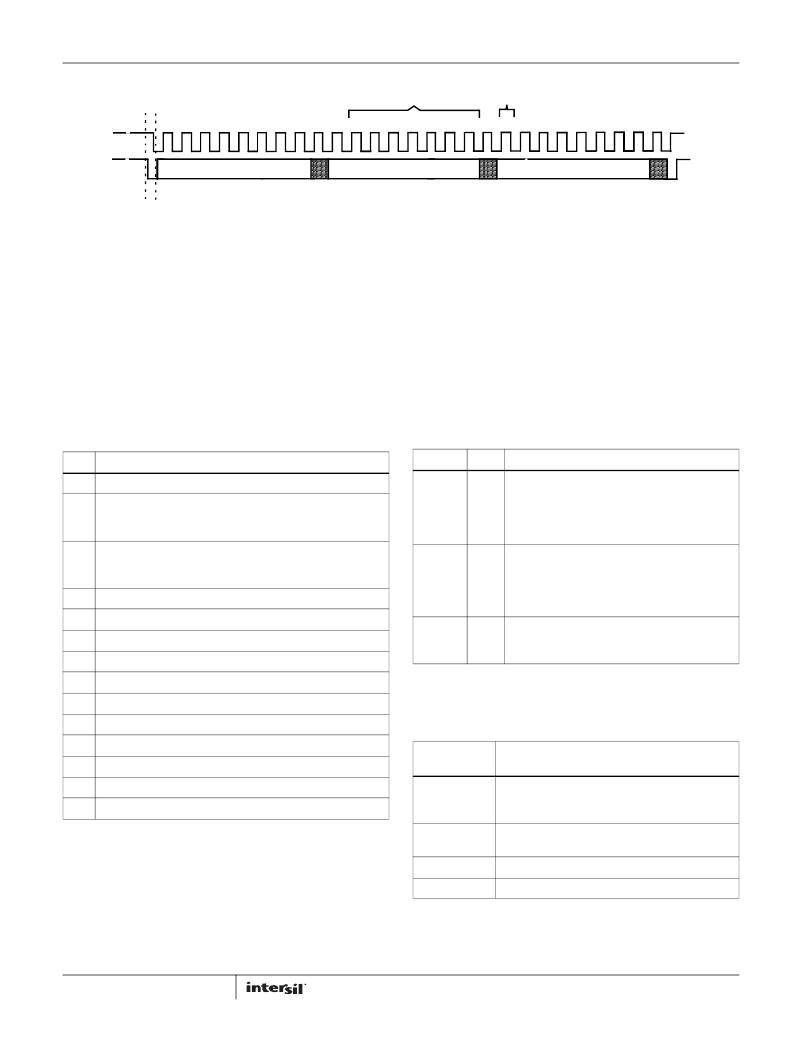

�FIGURE� 19.� SVD� PACKET� STRUCTURE�

�SVI� Bus� Protocol�

�The� AMD� processor� bus� protocol� is� compliant� with� SMBus� send�

�byte� protocol� for� VID� transactions.� The� AMD� SVD� packet� structure�

�is� shown� in� Figure� 19.� The� description� of� each� bit� of� the� three�

�bytes� that� make� up� the� SVI� command� are� shown� in� Table� 8.�

�During� a� transaction,� the� processor� sends� the� start� sequence�

�followed� by� each� of� the� three� bytes� which� end� with� an� optional�

�acknowledge� bit.� The� ISL6277� does� not� drive� the� SVD� line� during�

�the� ACK� bit.� Finally,� the� processor� sends� the� stop� sequence.� After�

�the� ISL6277� has� detected� the� stop,� it� can� then� proceed� with� the�

�commanded� action� from� the� transaction.�

�TABLE� 8.� SVD� DATA� PACKET�

�diode� emulation� mode� to� boost� efficiency.� When� PSI1_L� is�

�asserted� the� Core� VR� continues� to� operate� in� this� mode.�

�For� the� Northbridge� VR� operating� in� 2-phase� mode,� when� PSI0_L�

�is� asserted� Channel� 2� is� tri-stated� and� Channel� 1� enters� diode�

�emulation� mode� to� boost� efficiency.� When� PSI1_L� is� asserted� the�

�Core� VR� continues� to� operate� in� this� fashion.�

�It� is� possible� for� the� processor� to� assert� or� deassert� PSI0_L� and�

�PSI1_L� out� of� order.� PSI0_L� takes� priority� over� PSI1_L.� If� PSI0_L�

�is� deasserted� while� PSI1_L� is� still� asserted,� the� ISL6277� will�

�return� the� selected� VR� back� full� channel� CCM� operation.�

�TABLE� 9.� PSI0_L,� PSI1_L� AND� TFN� DEFINITION�

�BITS�

�1:5�

�6�

�7�

�8�

�9�

�10�

�DESCRIPTION�

�Always� 11000b�

�Core� domain� selector� bit,� if� set� then� the� following� data� byte�

�contains� VID,� power� state,� telemetry� control,� load� line� trim� and�

�offset� trim� apply� to� the� Core� VR.�

�Northbridge� domain� selector� bit,� if� set� then� the� following� data�

�byte� contains� VID,� power� state,� telemetry� control,� load� line� trim�

�and� offset� trim� apply� to� the� Northbridge� VR.�

�Always� 0b�

�Acknowledge� Bit�

�PSI0_L�

�FUNCTION�

�PSI0_L�

�PSI1_L�

�TFN�

�BIT�

�10�

�20�

�21�

�DESCRIPTION�

�Power� State� Indicate� level� 0.� When� this� signal� is�

�asserted� (active� Low)� the� processor� is� in� a� low�

�enough� power� state� for� the� ISL6277� to� take� action�

�to� boost� efficiency� by� dropping� phases� and� entering�

�1-Phase� DE.�

�Power� State� Indicate� level� 1.� When� this� signal� is�

�asserted� (active� Low)� the� processor� is� in� a� low�

�enough� power� state� for� the� ISL6277� to� take� action�

�to� boost� efficiency� by� dropping� phases� and� entering�

�1-Phase� DE.�

�Telemetry� Functionality.� This� is� an� active� high� signal�

�that� allows� the� processor� to� control� the� telemetry�

�11:17� VID� Code� bits� [7:1]�

�functionality� of� the� VR.�

�18�

�19�

�20�

�21�

�Acknowledge� Bit�

�VID� Code� bit� [0]�

�PSI1_L�

�TFN� (Telemetry� Functionality)�

�The� TFN� bit� along� with� the� Core� and� Northbridge� domain� selector�

�bits� are� used� by� the� processor� to� change� the� functionality� of�

�telemetry,� see� Table� 10� for� more� information.�

�TABLE� 10.� TFN� TRUTH� TABLE�

�TFN,� CORE,� NB�

�22:24� Load� Line� Slope� Trim�

�25:26� Offset� Trim� [1:0]�

�27� Acknowledge� Bit�

�Power� States� and� Telemetry�

�SVI2� defines� two� power� state� indicator� levels,� see� Table� 9.� As�

�processor� current� consumption� reduces� the� power� state� indicator�

�level� changes� to� improve� VR� efficiency� under� low� power�

�conditions.�

�For� the� Core� VR� operating� in� 3-phase� mode,� when� PSI0_L� is�

�asserted� Channels� 2� &� 3� are� tri-stated� and� Channel� 1� enters�

�25�

�BITS� [21,6,7]�

�1,0,1�

�1,0,0�

�1,1,0�

�1,1,1�

�DESCRIPTION�

�Telemetry� is� in� voltage� and� current� mode.� Therefore,�

�voltage� and� current� are� sent� for� VDD� and� VDDNB�

�domains� by� the� controller.�

�Telemetry� is� in� voltage� mode� only.� Only� the� voltage� of�

�VDD� and� VDDNB� domains� is� sent� by� the� controller.�

�Telemetry� is� disabled.�

�Reserved�

�FN8270.1�

�March� 8,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| HCC22DRXN | CONN EDGECARD 44POS DIP .100 SLD |

| ISL62773HRZ | IC PWM REG MULTIPH AMD 48-QFN |

| 400MXC390MEFCSN30X45 | CAP ALUM 390UF 400V 20% SNAP-IN |

| X40030V14I-A | IC VOLTAGE MONITOR TRPL 14-TSSOP |

| HCC22DRXH | CONN EDGECARD 44POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6277IRZ-T | 功能描述:IC PWM REG MULTIPH AMD 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL62810AHRUZ-T | 制造商:Intersil Corporation 功能描述:0/2-BIT PWM GPU CONTROLLER FOR NOTEBOOK. 20 LD 3.2 X 1.8 UTQ - Tape and Reel 制造商:Intersil 功能描述:0/2 BIT PWM GPU CONTLR FOR NOTEBOOK |

| ISL62810HRUZ-T | 制造商:Intersil Corporation 功能描述:0/2-BIT PWM GPU CONTROLLER FOR NOTEBOOK. 16LD 2.6 X 1.8 UTQF - Tape and Reel 制造商:Intersil 功能描述:0/2 BIT PWM GPU CONTLR FOR NOTEBOOK |

| ISL62870 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:PWM DC/DC Voltage Regulator Controller |

| ISL62870HRUZ | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:PWM DC/DC Voltage Regulator Controller |

发布紧急采购,3分钟左右您将得到回复。