参数资料

| 型号: | ISL6323BCRZ |

| 厂商: | Intersil |

| 文件页数: | 19/36页 |

| 文件大小: | 0K |

| 描述: | IC PWM CTRLR SYNC BUCK DL 48QFN |

| 标准包装: | 43 |

| 应用: | 控制器,AMD SVI |

| 输入电压: | 5 V ~ 12 V |

| 输出数: | 2 |

| 输出电压: | 最高 2V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�ISL6323B�

�TABLE� 4.� SERIAL� VID� CODES� (Continued)�

�SVID[6:0]�

�001_1011b�

�001_1100b�

�001_1101b�

�001_1110b�

�001_1111b�

�VOLTAGE� (V)�

�1.2125�

�1.2000�

�1.1875�

�1.1750�

�1.1625�

�SVID[6:0]�

�011_1011b�

�011_1100b�

�011_1101b�

�011_1110b�

�011_1111b�

�VOLTAGE� (V)�

�0.8125�

�0.8000�

�0.7875�

�0.7750�

�0.7625�

�SVID[6:0]�

�101_1011b�

�101_1100b�

�101_1101b�

�101_1110b�

�101_1111b�

�VOLTAGE� (V)�

�0.4125� *�

�0.4000� *�

�0.3875� *�

�0.3750� *�

�0.3625� *�

�SVID[6:0]�

�111_1011b�

�111_1100b�

�111_1101b�

�111_1110b�

�111_1111b�

�VOLTAGE� (V)�

�0.0125� *�

�OFF�

�OFF�

�OFF�

�OFF�

�NOTE:� *� Indicates� a� VID� not� required� for� AMD� Family� 10h� processors.�

�POWER� SAVINGS� MODE:� PSI_L�

�Bit� 7� of� the� Serial� VID� codes� transmitted� as� part� of� the� 8-bit�

�data� phase� over� the� SVI� bus� is� allocated� for� the� PSI_L.� If�

�Bit� 7� is� 0,� then� the� processor� is� at� an� optimal� load� for� the�

�regulator� to� enter� power� savings� mode.� If� Bit� 7� is� 1,� then� the�

�regulator� should� not� be� in� power� savings� mode.�

�With� the� ISL6323B,� Power� Savings� mode� is� realized� through�

�phase� shedding.� Once� a� Serial� VID� command� with� Bit� 7� set� to� 0�

�is� received,� the� ISL6323B� will� shed� all� phases� in� a� sequential�

�manner� until� only� Channel� 1� and� Channel� 2� are� switching.� If�

�active,� Channel� 4� will� be� shed� first,� followed� by� Channel� 3.�

�When� a� phase� is� shed,� that� phase� will� not� go� into� a� tri-state�

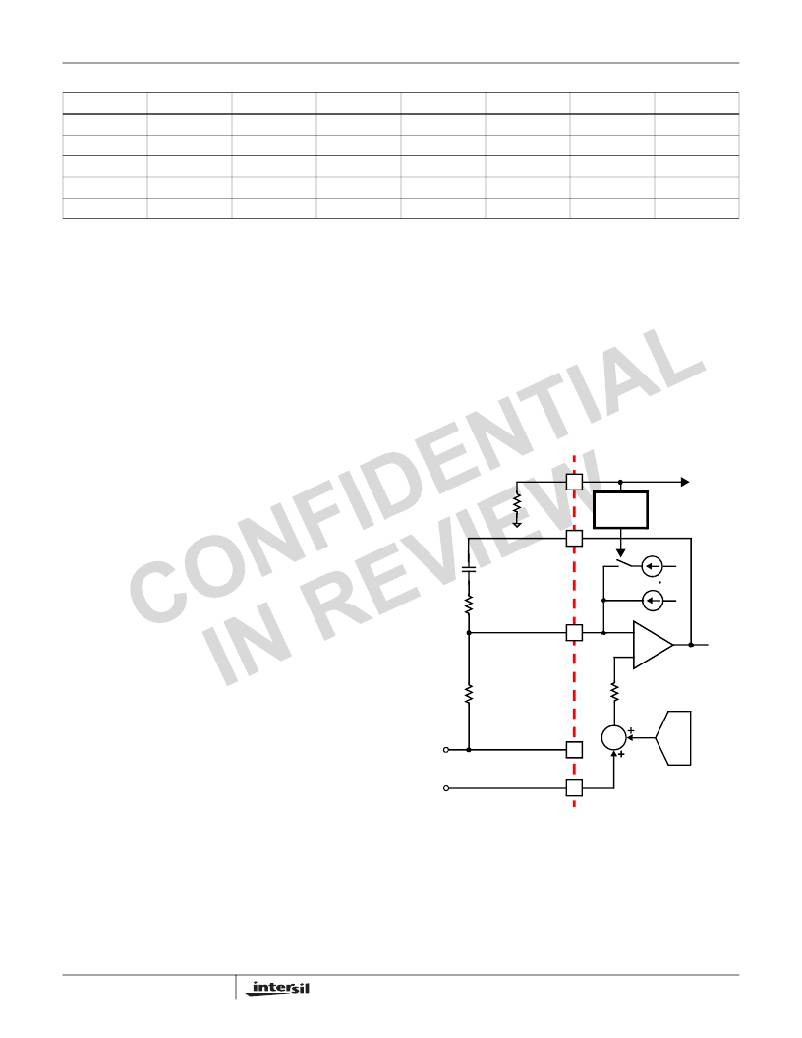

�The� ISL6323B� incorporates� differential� remote-sense�

�amplification� in� the� feedback� path.� The� differential� sensing�

�removes� the� voltage� error� encountered� when� measuring� the�

�output� voltage� relative� to� the� controller� ground� reference� point�

�resulting� in� a� more� accurate� means� of� sensing� output� voltage.�

�Load-Line� (Droop)� Regulation�

�By� adding� a� well� controlled� output� impedance,� the� output�

�voltage� can� effectively� be� level� shifted� in� a� direction� which�

�works� to� achieve� a� cost-effective� solution� can� help� to� reduce�

�the� output-voltage� spike� that� results� from� fast� load-current�

�demand� changes.�

�mode� until� that� phase� would� have� had� its� PWM� go� HIGH.�

�When� leaving� Power� Savings� Mode,� through� the� reception� of�

�EXTERNAL� CIRCUIT�

�FS�

�ISL6323B� INTERNAL� CIRCUIT�

�a� Serial� VID� command� with� Bit� 7� set� to� 1,� the� ISL6323B� will�

�sequentially� turn� on� phases� starting� with� Phase� 3.� When� a�

�phase� is� being� reactivated,� it� will� not� leave� a� tri-state� until� the�

�R� FS�

�COMP�

�DROOP�

�CONTROL�

�TO�

�OSCILLATOR�

�PWM� of� that� phase� goes� HIGH.�

�If,� while� in� Power� Savings� Mode,� a� Serial� VID� command� is�

�received� that� forces� a� VID� level� change� while� maintaining�

�Bit� 7� at� 0,� the� ISL6323B� will� first� exit� the� Power� Savings�

�C� C�

�R� C�

�8� I� AVG�

�Mode� state� as� described� above.� The� output� voltage� will� then�

�be� stepped� up� or� down� to� the� appropriate� VID� level.� Finally,�

�the� ISL6323B� will� then� re-enter� Power� Savings� Mode.�

�FB�

�-�

�+�

�I� OFS�

�ERROR�

�V� COMP�

�Voltage� Regulation�

�AMPLIFIER�

�The� integrating� compensation� network� shown� in� Figure� 8�

�insures� that� the� steady-state� error� in� the� output� voltage� is�

�R� FB�

�+�

�(V� DROOP� +� V� OFS� )�

�-�

�2k�

�limited� only� to� the� error� in� the� reference� voltage� and� offset�

�errors� in� the� OFS� current� source,� remote-sense� and� error�

�amplifiers.� Intersil� specifies� the� guaranteed� tolerance� of� the�

�ISL6323B� to� include� the� combined� tolerances� of� each� of�

�these� elements.�

�+�

�V� OUT�

�-�

�VSEN�

�RGND�

�∑�

�VID�

�DAC�

�V� OUT� =� V� REF� –� V� OFS� –� V� DROOP�

�The� output� of� the� error� amplifier,� V� COMP� ,� is� used� by� the�

�modulator� to� generate� the� PWM� signals.� The� PWM� signals�

�control� the� timing� of� the� Internal� MOSFET� drivers� and�

�regulate� the� converter� output� so� that� the� voltage� at� FB� is� equal�

�to� the� voltage� at� REF.� This� will� regulate� the� output� voltage� to�

�be� equal� to� Equation� 11.� The� internal� and� external� circuitry�

�that� controls� voltage� regulation� is� illustrated� in� Figure� 8.�

�(EQ.� 11)�

�19�

�FIGURE� 8.� OUTPUT� VOLTAGE� AND� LOAD-LINE�

�REGULATION� WITH� OFFSET� ADJUSTMENT�

�The� magnitude� of� the� spike� is� dictated� by� the� ESR� and� ESL�

�of� the� output� capacitors� selected.� By� positioning� the� no-load�

�voltage� level� near� the� upper� specification� limit,� a� larger�

�negative� spike� can� be� sustained� without� crossing� the� lower�

�limit.� By� adding� a� well� controlled� output� impedance,� the�

�output� voltage� under� load� can� effectively� be� level� shifted�

�FN6879.1�

�May� 12,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| RCA18DTMT | CONN EDGECARD 36POS R/A .125 SLD |

| ISL6323ACRZ | IC PWM CTRLR SYNC BUCK DL 48QFN |

| LD6806CX4/25H,315 | IC REG LDO 2.5V .2A 4WLCSP |

| 420USC390MEFCSN30X40 | CAP ALUM 390UF 420V 20% SNAP-IN |

| 2256-19L | POWER CHOKE 33UH MOLDED AXIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6323BCRZR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ SV - Rail/Tube 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BCRZ-T | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6323BCRZ-TR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ S - Tape and Reel 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BCRZ-TR5453 | 制造商:Intersil Corporation 功能描述:STD. ISL6323BCRZ-T WITH GOLD BOND WIRE ONLY, T&R - Tape and Reel |

| ISL6323BIRZ | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。