参数资料

| 型号: | ISL6323BCRZ |

| 厂商: | Intersil |

| 文件页数: | 23/36页 |

| 文件大小: | 0K |

| 描述: | IC PWM CTRLR SYNC BUCK DL 48QFN |

| 标准包装: | 43 |

| 应用: | 控制器,AMD SVI |

| 输入电压: | 5 V ~ 12 V |

| 输出数: | 2 |

| 输出电压: | 最高 2V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�ISL6323B�

�only� change� if� the� EN� signal� is� pulled� low� or� after� a� POR�

�reset� of� VCC.�

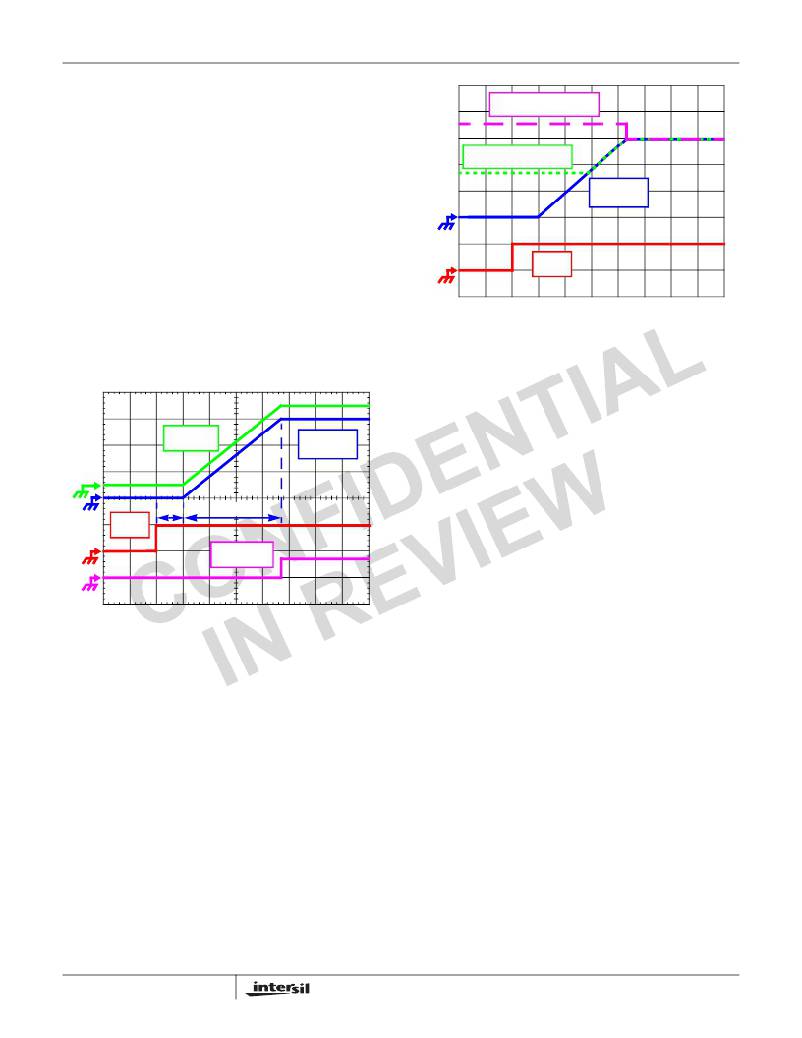

�OUTPUT� PRECHARGED�

�ABOVE� DAC� LEVEL�

�Soft-Start�

�The� soft-start� sequence� is� composed� of� three� periods,� as�

�shown� in� Figure� 13.� At� the� beginning� of� soft-start,� the� DAC�

�immediately� obtains� the� output� voltage� targets� for� both� outputs�

�by� decoding� the� state� of� the� SVI� or� PVI� inputs.� A� 100μs� fixed�

�delay� time,� TDA,� proceeds� the� output� voltage� rise.� After� this�

�delay� period� the� ISL6323B� will� begin� ramping� both� CORE� and�

�NB� output� voltages� to� the� programmed� DAC� level� at� a� fixed� rate�

�of� 3.25mV/μs.� The� amount� of� time� required� to� ramp� the� output�

�voltage� to� the� final� DAC� voltage� is� referred� to� as� TDB,� and� can�

�be� calculated� as� shown� in� Equation� 19.�

�OUTPUT� PRECHARGED�

�BELOW� DAC� LEVEL�

�EN�

�5V/DIV�

�V� CORE�

�400mV/DIV�

�V� DAC�

�3.25� � 10�

�TDB� =� ------------------------------�

�–� 3�

�(EQ.� 19)�

�100μs/DIV�

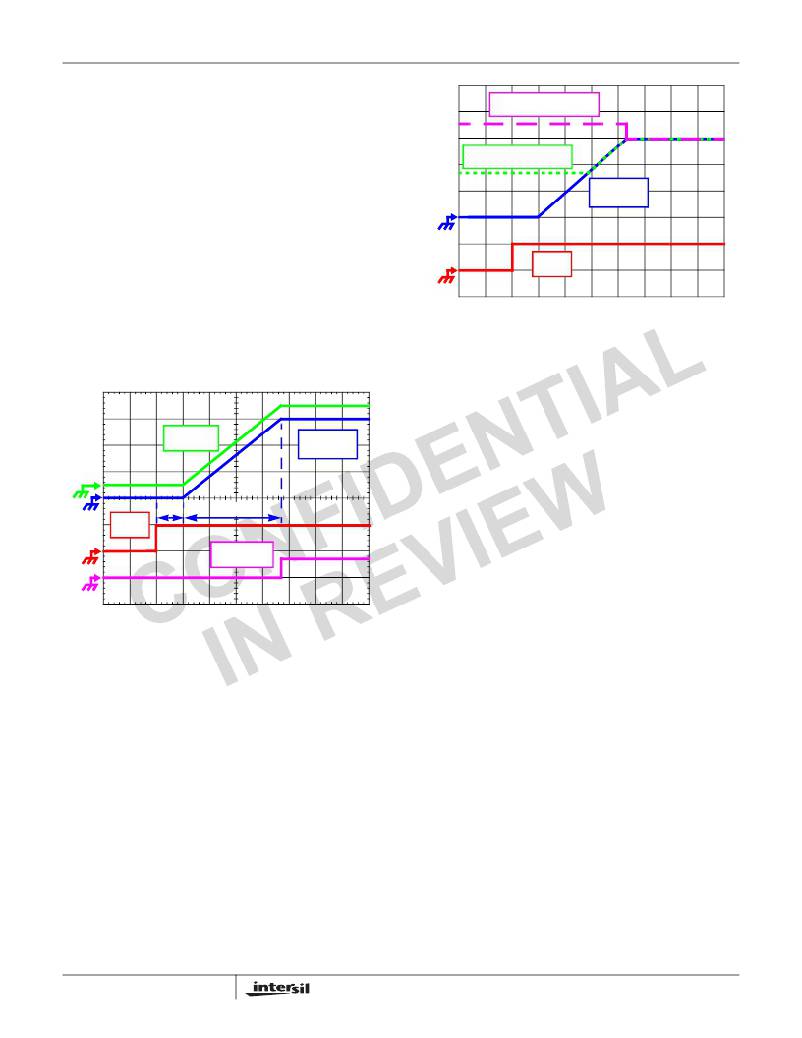

�FIGURE� 14.� SOFT-START� WAVEFORMS� FOR�

�ISL6323B-BASED� MULTI-PHASE� CONVERTER�

�After� the� DAC� voltage� reaches� the� final� VID� setting,� PGOOD�

�will� be� set� to� high.�

�Fault� Monitoring� and� Protection�

�The� ISL6323B� actively� monitors� both� CORE� and� NB� output�

�voltages� and� currents� to� detect� fault� conditions.� Fault�

�monitors� trigger� protective� measures� to� prevent� damage� to�

�V� NB�

�400mV/DIV�

�TDA�

�TDB�

�V� CORE�

�400mV/DIV�

�either� load.� One� common� power� good� indicator� is� provided�

�for� linking� to� external� system� monitors.� The� schematic� in�

�Figure� 15� outlines� the� interaction� between� the� fault� monitors�

�and� the� power� good� signal.�

�Power-Good� Signal�

�EN�

�5V/DIV�

�VDDPWRGD�

�5V/DIV�

�100μs/DIV�

�FIGURE� 13.� SOFT-START� WAVEFORMS�

�Pre-Biased� Soft-Start�

�The� ISL6323B� also� has� the� ability� to� start� up� into� a�

�pre-charged� output,� without� causing� any� unnecessary�

�disturbance.� The� FB� pin� is� monitored� during� soft-start,� and�

�should� it� be� higher� than� the� equivalent� internal� ramping�

�reference� voltage,� the� output� drives� hold� both� MOSFETs� off.�

�Once� the� internal� ramping� reference� exceeds� the� FB� pin�

�potential,� the� output� drives� are� enabled,� allowing� the� output�

�to� ramp� from� the� pre-charged� level� to� the� final� level� dictated�

�by� the� DAC� setting.� Should� the� output� be� pre-charged� to� a�

�level� exceeding� the� DAC� setting,� the� output� drives� are�

�enabled� at� the� end� of� the� soft-start� period,� leading� to� an�

�abrupt� correction� in� the� output� voltage� down� to� the� DAC-set�

�level.� Both� CORE� and� NB� output� support� start� up� into� a�

�pre-charged� output.�

�23�

�The� power-good� pin� (VDDPWRGD)� is� an� open-drain� logic�

�output� that� signals� whether� or� not� the� ISL6323B� is� regulating�

�both� NB� and� CORE� output� voltages� within� the� proper� levels,�

�and� whether� any� fault� conditions� exist.� This� pin� should� be�

�tied� to� a� +5V� source� through� a� resistor.�

�During� shutdown� and� soft-start,� VDDPWRGD� pulls� low� and�

�releases� high� after� a� successful� soft-start� and� both� output�

�voltages� are� operating� between� the� undervoltage� and�

�overvoltage� limits.� PGOOD� transitions� low� when� an�

�undervoltage,� overvoltage,� or� overcurrent� condition� is� detected�

�on� either� regulator� output� or� when� the� controller� is� disabled� by� a�

�POR� reset� or� EN.� In� the� event� of� an� overvoltage� or� overcurrent�

�condition,� the� controller� latches� off� and� PGOOD� will� not� return�

�high.� Pending� a� POR� reset� of� the� ISL6323B� and� successful�

�soft-start,� the� PGOOD� will� return� high.�

�Overvoltage� Protection�

�The� ISL6323B� constantly� monitors� the� sensed� output� voltage�

�on� the� VSEN� pin� to� detect� if� an� overvoltage� event� occurs.�

�When� the� output� voltage� rises� above� the� OVP� trip� level� and�

�exceeds� the� PGOOD� OV� limit� actions� are� taken� by� the�

�ISL6323B� to� protect� the� microprocessor� load.�

�At� the� inception� of� an� overvoltage� event,� both� on-board� lower�

�gate� pins� are� commanded� low� as� are� the� active� PWM� outputs�

�to� the� external� drivers,� the� PGOOD� signal� is� driven� low,� and� the�

�ISL6323B� latches� off� normal� PWM� action.� This� turns� on� the� all�

�of� the� lower� MOSFETs� and� pulls� the� output� voltage� below� a�

�FN6879.1�

�May� 12,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| RCA18DTMT | CONN EDGECARD 36POS R/A .125 SLD |

| ISL6323ACRZ | IC PWM CTRLR SYNC BUCK DL 48QFN |

| LD6806CX4/25H,315 | IC REG LDO 2.5V .2A 4WLCSP |

| 420USC390MEFCSN30X40 | CAP ALUM 390UF 420V 20% SNAP-IN |

| 2256-19L | POWER CHOKE 33UH MOLDED AXIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6323BCRZR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ SV - Rail/Tube 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BCRZ-T | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6323BCRZ-TR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ S - Tape and Reel 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BCRZ-TR5453 | 制造商:Intersil Corporation 功能描述:STD. ISL6323BCRZ-T WITH GOLD BOND WIRE ONLY, T&R - Tape and Reel |

| ISL6323BIRZ | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。