参数资料

| 型号: | ISL6323BCRZ |

| 厂商: | Intersil |

| 文件页数: | 22/36页 |

| 文件大小: | 0K |

| 描述: | IC PWM CTRLR SYNC BUCK DL 48QFN |

| 标准包装: | 43 |

| 应用: | 控制器,AMD SVI |

| 输入电压: | 5 V ~ 12 V |

| 输出数: | 2 |

| 输出电压: | 最高 2V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�ISL6323B�

�above� the� PHASE� or� the� PHASE� falls� to� less� than� +0.8V,� the�

�LGATE� is� released� to� turn-on.�

�Initialization�

�Prior� to� initialization,� proper� conditions� must� exist� on� the� EN,�

�VCC,� PVCC1_2,� PVCC_NB,� ISEN3-,� and� ISEN4-� pins.� When�

�the� conditions� are� met,� the� controller� begins� soft-start.� Once�

�the� output� voltage� is� within� the� proper� window� of� operation,�

�the� controller� asserts� PGOOD.�

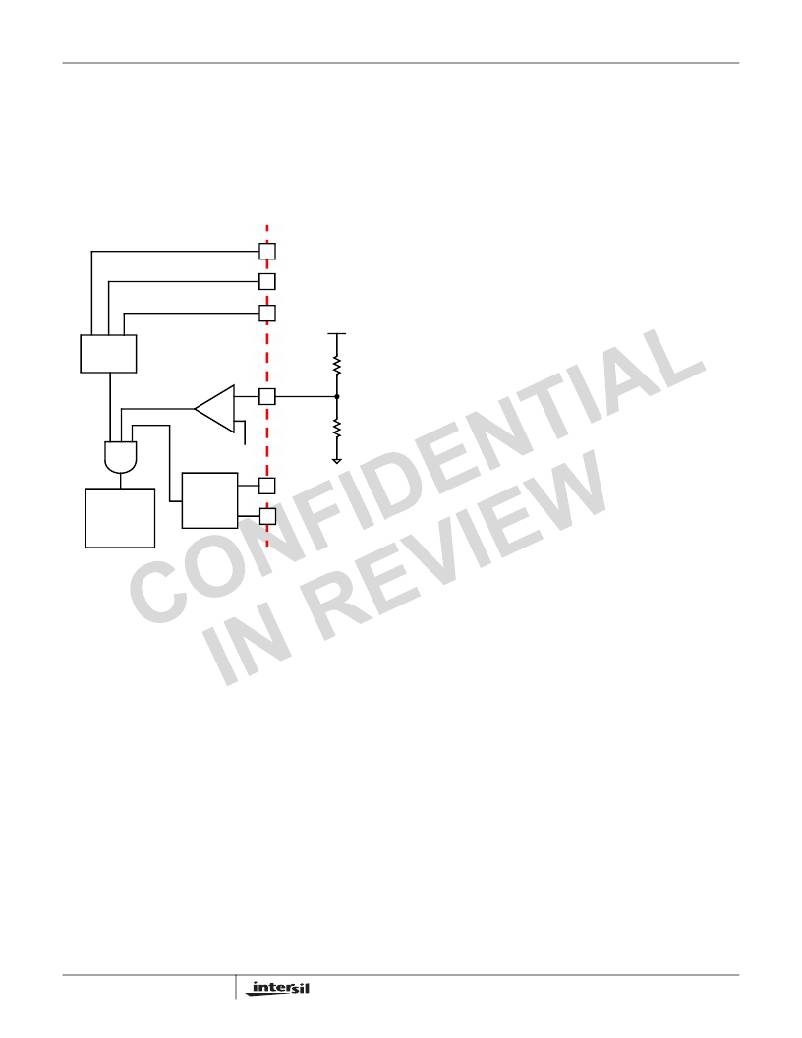

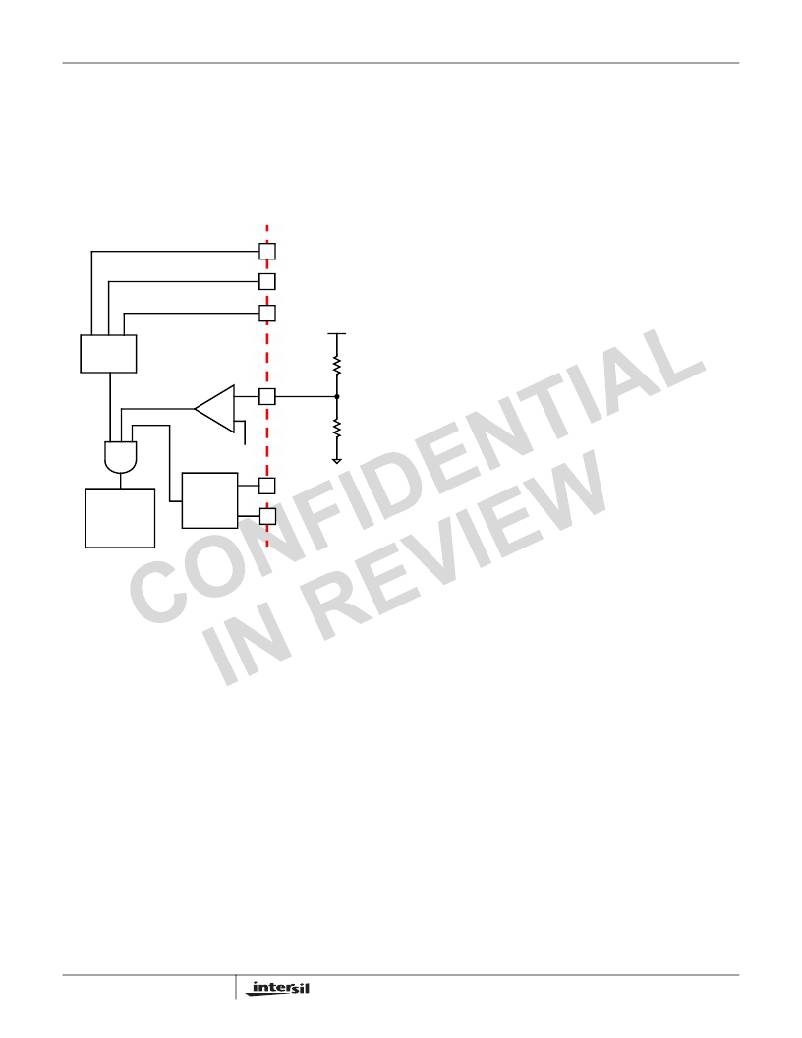

�ISL6323B� INTERNAL� CIRCUIT� EXTERNAL� CIRCUIT�

�VCC�

�PVCC1_2�

�Detect� block,� the� external� driver� POR� checking� is� supported�

�by� the� Enable� Comparator.�

�Enable� Comparator�

�The� ISL6323B� features� a� dual� function� enable� input� (EN)� for�

�enabling� the� controller� and� power� sequencing� between� the�

�controller� and� external� drivers� or� another� voltage� rail.� The�

�enable� comparator� holds� the� ISL6323B� in� shutdown� until� the�

�voltage� at� EN� rises� above� 0.86V.� The� enable� comparator� has�

�about� 110mV� of� hysteresis� to� prevent� bounce.� It� is� important�

�that� the� driver� ICs� reach� their� rising� POR� level� before� the�

�ISL6323B� becomes� enabled.� The� schematic� in� Figure� 12�

�demonstrates� sequencing� the� ISL6323B� with� the� ISL66xx�

�family� of� Intersil� MOSFET� drivers,� which� require� 12V� bias.�

�PVCC_NB�

�+� 12� V�

�When� selecting� the� value� of� the� resistor� divider� the� driver�

�maximum� rising� POR� threshold� should� be� used� for� calculating�

�POR�

�CIRCUIT�

�ENABLE�

�COMPARATOR�

�+�

�-�

�EN�

�10.7k� Ω�

�1.00k� Ω�

�the� proper� resistor� values.� This� will� prevent� improper�

�sequencing� events� from� creating� false� trips� during� soft-start.�

�If� the� controller� is� configured� for� 2-phase� CORE� operation,�

�then� the� resistor� divider� can� be� used� for� sequencing� the�

�controller� with� another� voltage� rail.� The� resistor� divider� to� EN�

�should� be� selected� using� a� similar� approach� as� the� previous�

�driver� discussion.�

�0.86V�

�The� EN� pin� is� also� used� to� force� the� ISL6323B� into� either�

�CHANNEL�

�ISEN3-�

�PVI� or� SVI� mode.� The� mode� is� set� upon� the� rising� edge� of�

�the� EN� signal.� When� the� voltage� on� the� EN� pin� rises� above�

�SOFT-START�

�AND�

�FAULT� LOGIC�

�DETECT�

�ISEN4-�

�0.86V,� the� mode� will� be� set� depending� upon� the� status� of� the�

�VID1/SEL� pin.�

�FIGURE� 12.� POWER� SEQUENCING� USING� THRESHOLD-�

�SENSITIVE� ENABLE� (EN)� FUNCTION�

�Power-On� Reset�

�The� ISL6323B� requires� VCC,� PVCC1_2,� and� PVCC_NB�

�inputs� to� exceed� their� rising� POR� thresholds� before� the�

�ISL6323B� has� sufficient� bias� to� guarantee� proper� operation.�

�The� bias� voltage� applied� to� VCC� must� reach� the� internal�

�power-on� reset� (POR)� rising� threshold.� Once� this� threshold�

�is� reached,� the� ISL6323B� has� enough� bias� to� begin� checking�

�the� driver� POR� inputs,� EN,� and� channel� detect� portions� of�

�the� initialization� cycle.� Hysteresis� between� the� rising� and�

�falling� thresholds� assure� the� ISL6323B� will� not� advertently�

�turn� off� unless� the� bias� voltage� drops� substantially� (see�

�Electrical� Specifications� on� page� 9).�

�The� bias� voltage� applied� to� the� PVCC1_2� and� PVCC_NB�

�pins� power� the� internal� MOSFET� drivers� of� each� output�

�channel.� In� order� for� the� ISL6323B� to� begin� operation,� both�

�PVCC� inputs� must� exceed� their� POR� rising� threshold� to�

�guarantee� proper� operation� of� the� internal� drivers.�

�Hysteresis� between� the� rising� and� falling� thresholds� assure�

�that� once� enabled,� the� ISL6323B� will� not� inadvertently� turn�

�off� unless� the� PVCC� bias� voltage� drops� substantially� (see�

�Electrical� Specifications� on� page� 9).� Depending� on� the�

�number� of� active� CORE� channels� determined� by� the� Phase�

�22�

�Phase� Detection�

�The� ISEN3-� and� ISEN4-� pins� are� monitored� prior� to� soft-start�

�to� determine� the� number� of� active� CORE� channel� phases.�

�If� ISEN4-� is� tied� to� VCC,� the� controller� will� configure� the�

�channel� firing� order� and� timing� for� 3-phase� operation.� If�

�ISEN3-� and� ISEN4-� are� tied� to� VCC,� the� controller� will� set�

�the� channel� firing� order� and� timing� for� 2-phase� operation�

�(see� “PWM� Operation”� on� page� 14� for� details).�

�Soft-Start� Output� Voltage� Targets�

�Once� the� POR� and� Phase� Detect� blocks� and� enable�

�comparator� are� satisfied,� the� controller� will� begin� the�

�soft-start� sequence� and� will� ramp� the� CORE� and� NB� output�

�voltages� up� to� the� SVI� interface� designated� target� level� if� the�

�controller� is� set� SVI� mode.� If� set� to� PVI� mode,� the� North�

�Bridge� regulator� is� disabled� and� the� core� is� soft� started� to� the�

�level� designated� by� the� parallel� VID� code.�

�SVI� Mode�

�Prior� to� soft-starting� both� CORE� and� NB� outputs,� the�

�ISL6323B� must� check� the� state� of� the� SVI� interface� inputs� to�

�determine� the� correct� target� voltages� for� both� outputs.� When�

�the� controller� is� enabled,� the� state� of� the� VFIXEN,� SVD� and�

�SVC� inputs� are� checked� and� the� target� output� voltages� set�

�for� both� CORE� and� NB� outputs� are� set� by� the� DAC� (see�

��FN6879.1�

�May� 12,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| RCA18DTMT | CONN EDGECARD 36POS R/A .125 SLD |

| ISL6323ACRZ | IC PWM CTRLR SYNC BUCK DL 48QFN |

| LD6806CX4/25H,315 | IC REG LDO 2.5V .2A 4WLCSP |

| 420USC390MEFCSN30X40 | CAP ALUM 390UF 420V 20% SNAP-IN |

| 2256-19L | POWER CHOKE 33UH MOLDED AXIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6323BCRZR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ SV - Rail/Tube 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BCRZ-T | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6323BCRZ-TR5381 | 制造商:Intersil Corporation 功能描述:4+1 PHASE CONT. FOR CORE+NORTHBRIDGE, 2 PHASE PSI, 3.4MHZ S - Tape and Reel 制造商:Intersil Corporation 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN 制造商:Intersil 功能描述:4+1 PHS CONT CORE + NORTHBRDG PROG |

| ISL6323BCRZ-TR5453 | 制造商:Intersil Corporation 功能描述:STD. ISL6323BCRZ-T WITH GOLD BOND WIRE ONLY, T&R - Tape and Reel |

| ISL6323BIRZ | 功能描述:IC PWM CTRLR SYNC BUCK DL 48QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。