参数资料

| 型号: | ISL6545IBZ-T |

| 厂商: | Intersil |

| 文件页数: | 6/16页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 8-SOIC |

| 标准包装: | 1 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 330kHz |

| 占空比: | 100% |

| 电源电压: | 4.5 V ~ 14.4 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 包装: | 标准包装 |

| 产品目录页面: | 1243 (CN2011-ZH PDF) |

| 其它名称: | ISL6545IBZ-TDKR |

�� �

�

�

�ISL6545,� ISL6545A�

�Functional� Description�

�Initialization� (POR� and� OCP� Sampling)�

�Figure� 1� shows� a� simplified� timing� diagram.� The�

�Power-On-Reset� (POR)� function� continually� monitors� the�

�bias� voltage� at� the� VCC� pin.� Once� the� rising� POR� threshold�

�is� exceeded� (VPOR� ~4V� nominal),� the� POR� function� initiates�

�the� Overcurrent� Protection� (OCP)� sample� and� hold�

�soft-start� operation� is� initiated,� and� the� output� voltage� ramps�

�up� between� t4� and� t5.�

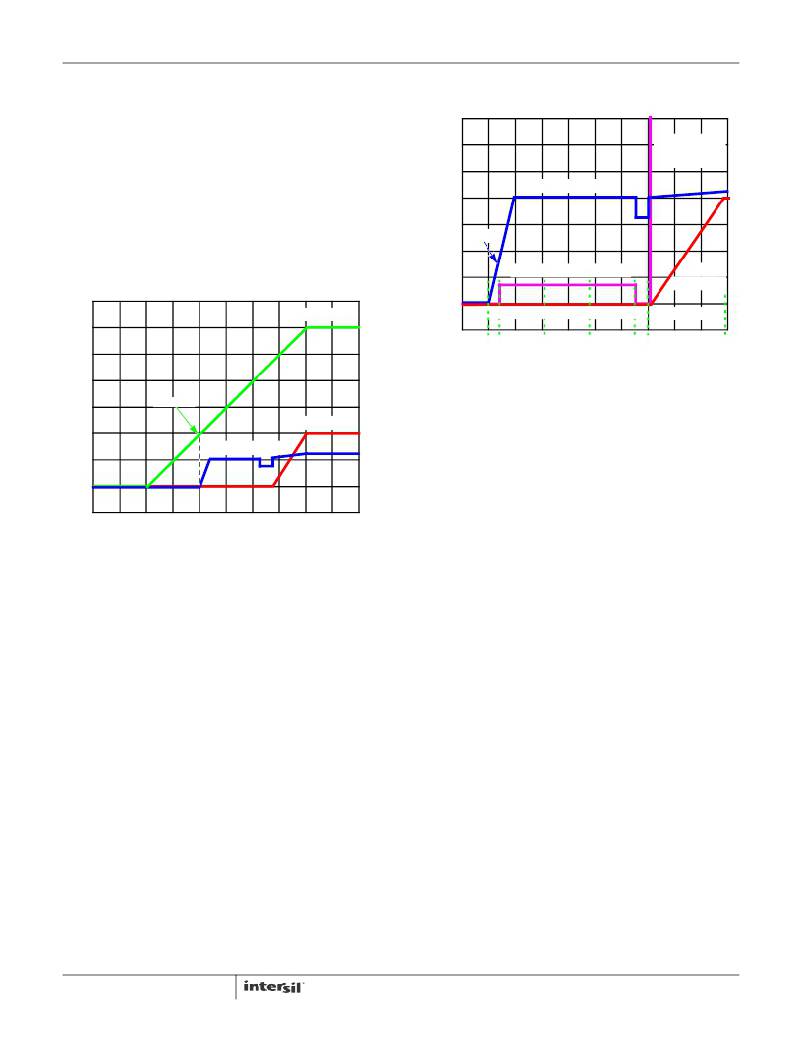

�LGATE�

�STARTS�

�SWITCHING�

�COMP/SD (0.25V/DIV)�

�operation� (while� COMP/SD� is� ~1V).� When� the� sampling� is�

�complete,� VOUT� begins� the� soft-start� ramp.�

�0.4V�

�If� the� COMP/SD� pin� is� held� low� during� power-up,� that� will� just�

�delay� the� initialization� until� it� is� released,� and� the� COMP/SD�

�voltage� is� above� the� V� DISABLE� trip� point.�

�LGATE/OCSET (0.25V/DIV)�

�V� OUT�

�(0.5V/DIV)�

�V� CC� (2V/DIV)�

�GND>�

�3.4ms�

�t0� t1�

�3.4ms�

�0� -� 3.4ms�

�t2�

�t3� t4�

�6.8ms�

�t5�

�FIGURE� 2.� LGATE/OCSET� AND� SOFT-START� OPERATION�

�Soft-Start� and� Pre-Biased� Outputs�

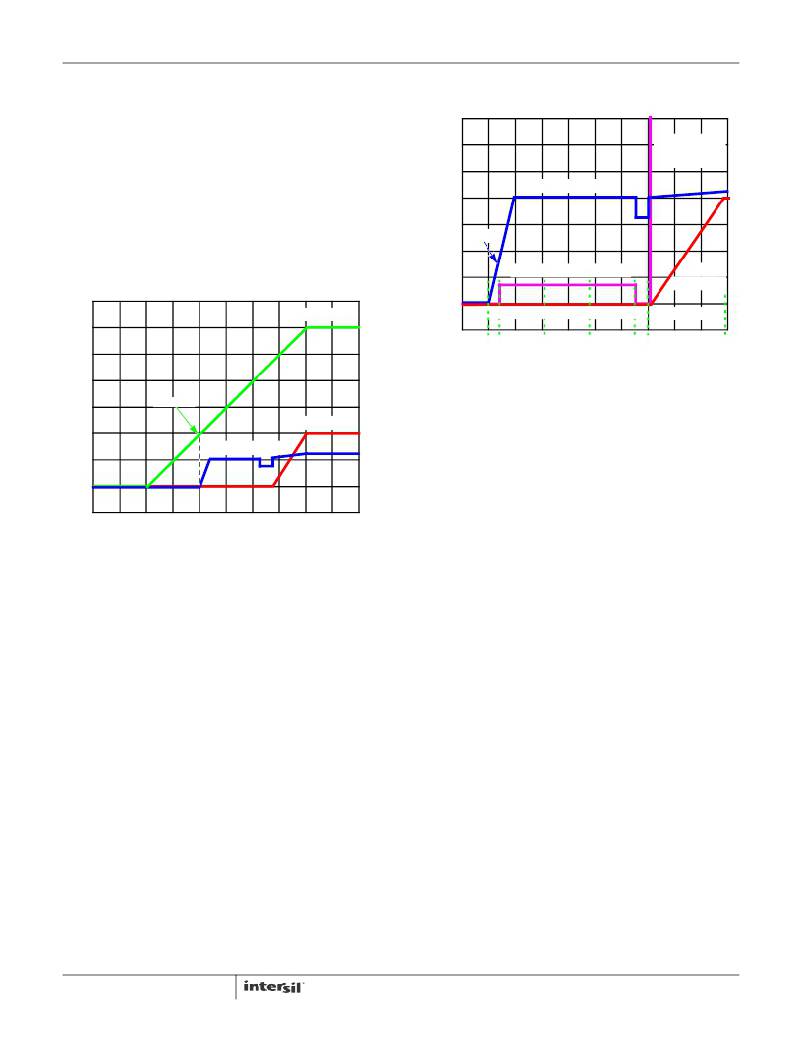

�~4V POR�

�V� OUT� (1V/DIV)�

�COMP/SD� (1V/DIV)�

�GND>�

�FIGURE� 1.� POR� AND� SOFT-START� OPERATION�

�Figure� 2� shows� a� typical� power-up� sequence� in� more� detail.�

�The� initialization� starts� at� T0,� when� either� V� CC� rises� above�

�V� POR� ,� or� the� COMP/SD� pin� is� released� (after� POR).� The�

�COMP/SD� will� be� pulled� up� by� an� internal� 20μA� current�

�source,� but� the� timing� will� not� begin� until� the� COMP/SD�

�exceeds� the� V� DISABLE� trip� point� (at� t1).� The� external�

�capacitance� of� the� disabling� device,� as� well� as� the�

�compensation� capacitors,� will� determine� how� quickly� the�

�20μA� current� source� will� charge� the� COMP/SD� pin.� With�

�typical� values,� it� should� add� a� small� delay� compared� to� the�

�soft-start� times.� The� COMP/SD� will� continue� to� ramp� to� ~1V.�

�From� t1,� there� is� a� nominal� 6.8ms� delay,� which� allows� the�

�V� CC� pin� to� exceed� 6.5V� (if� rising� up� towards� 12V),� so� that�

�the� internal� bias� regulator� can� turn� on� cleanly.� At� the� same�

�time,� the� LGATE/OCSET� pin� is� initialized,� by� disabling� the�

�LGATE� driver� and� drawing� I� OCSET� (nominal� 21.5μA)�

�through� R� OCSET� .� This� sets� up� a� voltage� that� will� represent�

�the� OCSET� trip� point.� At� t2,� there� is� a� variable� time� period� for�

�the� OCP� sample� and� hold� operation� (0ms� to� 3.4ms� nominal;�

�the� longer� time� occurs� with� the� higher� overcurrent� setting).�

�The� sample� and� hold� uses� a� digital� counter� and� DAC� to� save�

�the� voltage,� so� the� stored� value� does� not� degrade,� for� as�

�long� as� the� V� CC� is� above� V� POR� .� See� “Overcurrent� Protection�

��variables.� Upon� the� completion� of� sample� and� hold� at� t3,� the�

�6�

�Functionally,� the� soft-start� internally� ramps� the� reference� on�

�the� non-inverting� terminal� of� the� error� amp� from� 0V� to� 0.6V� in�

�a� nominal� 6.8ms� The� output� voltage� will� thus� follow� the�

�ramp,� from� zero� to� final� value,� in� the� same� 6.8ms� (the� actual�

�ramp� seen� on� the� V� OUT� will� be� less� than� the� nominal� time,�

�due� to� some� initialization� timing,� between� t3� and� t4).�

�The� ramp� is� created� digitally,� so� there� will� be� 64� small�

�discrete� steps.� There� is� no� simple� way� to� change� this� ramp�

�rate� externally,� and� it� is� the� same� for� either� frequency�

�version� of� the� IC� (300kHz� or� 600kHz).�

�After� an� initialization� period� (t3� to� t4),� the� error� amplifier�

�(COMP/SD� pin)� is� enabled,� and� begins� to� regulate� the�

�converter� ’s� output� voltage� during� soft-start.� The� oscillator� ’s�

�triangular� waveform� is� compared� to� the� ramping� error�

�amplifier� voltage.� This� generates� PHASE� pulses� of�

�increasing� width� that� charge� the� output� capacitors.� When� the�

�internally� generated� soft-start� voltage� exceeds� the� reference�

�voltage� (0.6V),� the� soft-start� is� complete,� and� the� output�

�should� be� in� regulation� at� the� expected� voltage.� This� method�

�provides� a� rapid� and� controlled� output� voltage� rise;� there� is�

�no� large� inrush� current� charging� the� output� capacitors.� The�

�entire� start-up� sequence� from� POR� typically� takes� up� to�

�17ms;� up� to� 10.2ms� for� the� delay� and� OCP� sample,� and�

�6.8ms� for� the� soft-start� ramp.�

�Figure� 3� shows� the� normal� curve� in� blue;� initialization� begins�

�at� t0,� and� the� output� ramps� between� t1� and� t2.� If� the� output� is�

�pre-biased� to� a� voltage� less� than� the� expected� value,� as�

�shown� by� the� magenta� curve,� the� ISL6545x� will� detect� that�

�condition.� Neither� MOSFET� will� turn� on� until� the� soft-start�

�ramp� voltage� exceeds� the� output;� V� OUT� starts� seamlessly�

�ramping� from� there.� If� the� output� is� pre-biased� to� a� voltage�

�above� the� expected� value,� as� in� the� red� curve,� neither�

�MOSFET� will� turn� on� until� the� end� of� the� soft-start,� at� which�

�FN6305.6�

�March� 3,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6548ACRZA-T | IC REG/CTLR ACPI DUAL DDR 28QFN |

| ISL6548CRZA | IC REG/CTRLR ACPI DUAL DDR 28QFN |

| ISL6551IR-T | IC REG CTRLR FLYBACK PWM 28-QFN |

| ISL6552CR-T | IC REG CTRLR BUCK PWM 20-QFN |

| ISL6553CB-T | IC REG CTRLR BUCK PWM 16-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6545IRZ | 功能描述:IC REG CTRLR BUCK PWM VM 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6545IRZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6546IRZ | 功能描述:IC REG BUCK SYNC 1.2A 10-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:降压(降压) 输出类型:固定 输出数:1 输出电压:3.3V 输入电压:4.5 V ~ 24 V PWM 型:- 频率 - 开关:- 电流 - 输出:125mA 同步整流器:无 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SOT-23-6 包装:Digi-Reel® 供应商设备封装:SOT-6 其它名称:MAX1836EUT33#TG16DKR |

| ISL6546IRZ-T | 功能描述:IC REG BUCK SYNC 1.2A 10-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:降压(降压) 输出类型:固定 输出数:1 输出电压:3.3V 输入电压:4.5 V ~ 24 V PWM 型:- 频率 - 开关:- 电流 - 输出:125mA 同步整流器:无 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SOT-23-6 包装:Digi-Reel® 供应商设备封装:SOT-6 其它名称:MAX1836EUT33#TG16DKR |

| ISL6548A-6506EVAL1Z | 功能描述:EVALUATION BOARD ISL6548A-6506 RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

发布紧急采购,3分钟左右您将得到回复。