参数资料

| 型号: | ISL6566CR |

| 厂商: | Intersil |

| 文件页数: | 19/29页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM BUCK 3PHASE 40-QFN |

| 标准包装: | 50 |

| 应用: | 控制器,Intel VRM9,VRM10,AMD Hammer 应用 |

| 输入电压: | 3 V ~ 12 V |

| 输出数: | 1 |

| 输出电压: | 0.8 V ~ 1.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘 |

| 供应商设备封装: | 40-QFN(6x6) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

�� �

�

�

�ISL6566�

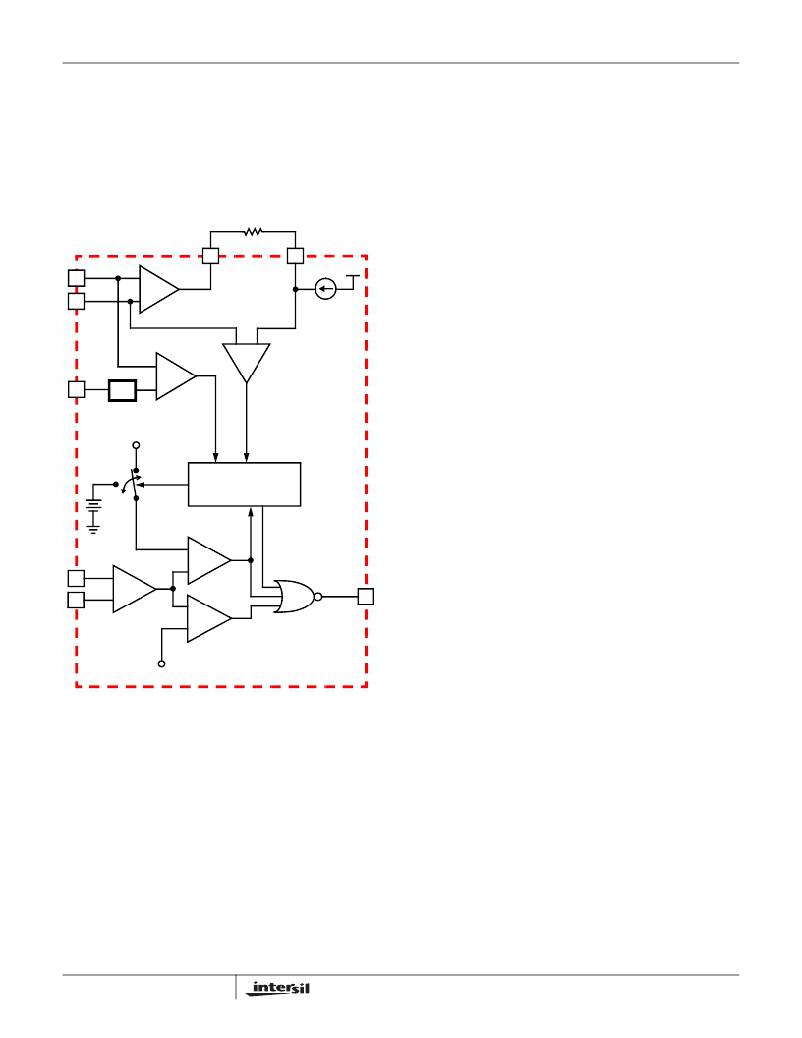

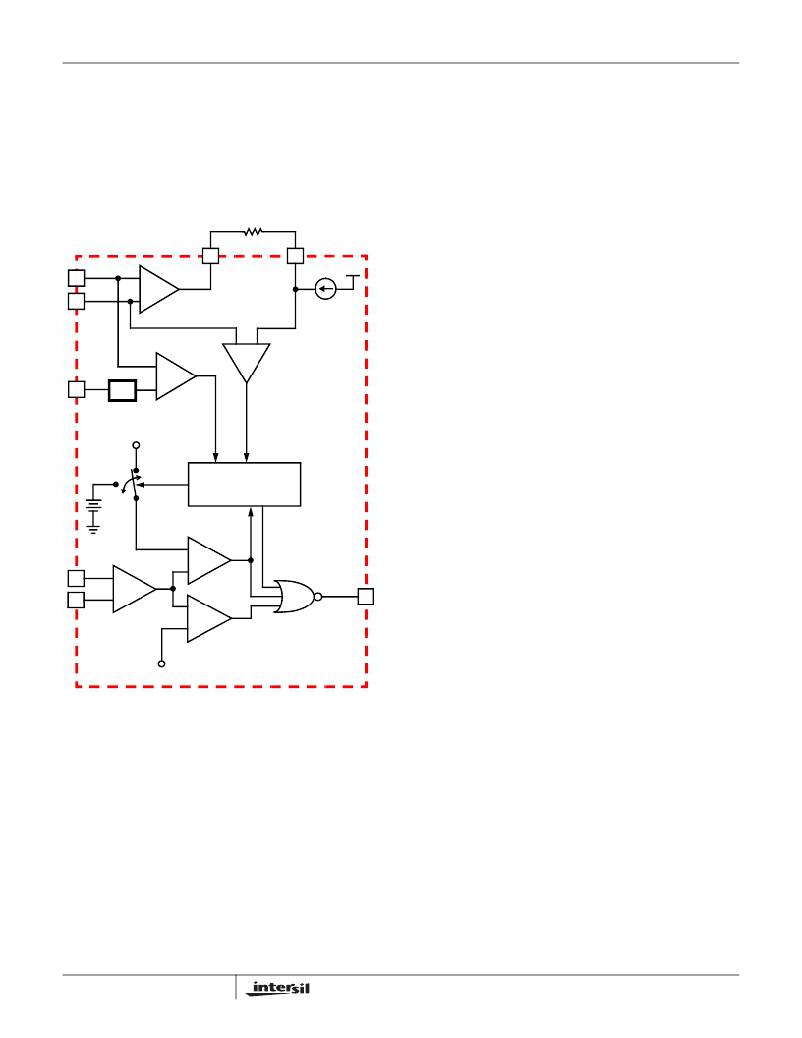

�Fault� Monitoring� and� Protection�

�The� ISL6566� actively� monitors� output� voltage� and� current� to�

�detect� fault� conditions.� Fault� monitors� trigger� protective�

�measures� to� prevent� damage� to� a� microprocessor� load.� One�

�common� power� good� indicator� is� provided� for� linking� to�

�external� system� monitors.� The� schematic� in� Figure� 13�

�outlines� the� interaction� between� the� fault� monitors� and� the�

�power� good� signal.�

�R� OCSET�

�Undervoltage� Detection�

�The� undervoltage� threshold� is� set� at� 82%� of� the� VID� code.�

�When� the� output� voltage� (VSEN-RGND)� is� below� the�

�undervoltage� threshold,� PGOOD� gets� pulled� low.� No� other�

�action� is� taken� by� the� controller.� PGOOD� will� return� high� if�

�the� output� voltage� rises� above� 85%� of� the� VID� code.�

�Overvoltage� Protection�

�The� ISL6566� constantly� monitors� the� difference� between� the�

�VSEN� and� RGND� voltages� to� detect� if� an� overvoltage� event�

�IREF�

�ISUM�

�+�

�ISEN�

�-�

�ICOMP�

�-�

�V� DROOP�

�+�

�-�

�V� OCSET�

�+�

�OCSET�

�100uA�

�occurs.� During� soft-start,� while� the� DAC� is� ramping� up,� the�

�overvoltage� trip� level� is� the� higher� of� DAC� plus� 150mV� or� a�

�fixed� voltage,� V� OVP� .� The� fixed� voltage,� V� OVP� ,� is� 1.67V� when�

�running� in� AMD� Hammer,� or� VRM10� modes,� and� 1.97V� for�

�VRM9� mode.� Upon� successful� soft-start,� the� overvoltage� trip�

�level� is� only� DAC� plus� 150mV.� OVP� releases� 50mV� below� its�

�trip� point� if� it� was� “DAC� plus� 150mV”� that� tripped� it,� and�

�VDIFF�

�+1V�

�+�

�-�

�OC�

�releases� 100mV� below� its� trip� point� if� it� was� the� fixed� voltage,�

�V� OVP� ,� that� tripped� it.� Actions� are� taken� by� the� ISL6566� to�

�protect� the� microprocessor� load� when� an� overvoltage�

�condition� occurs,� until� the� output� voltage� falls� back� within� set�

�limits.�

�VID� +� 150mV�

�At� the� inception� of� an� overvoltage� event,� all� LGATE� signals�

�are� commanded� high,� and� the� PGOOD� signal� is� driven� low.�

�V� OVP�

�SOFT-START,� FAULT�

�AND� CONTROL� LOGIC�

�-�

�This� causes� the� controller� to� turn� on� the� lower� MOSFETs�

�and� pull� the� output� voltage� below� a� level� that� might� cause�

�damage� to� the� load.� The� LGATE� outputs� remain� high� until�

�VDIFF� falls� to� within� the� overvoltage� limits� explained� above.�

�The� ISL6566� will� continue� to� protect� the� load� in� this� fashion�

�as� long� as� the� overvoltage� condition� recurs.�

�VSEN�

�RGND�

�+�

�-�

�x1�

�+�

�-�

�+�

�OV�

�UV�

�PGOOD�

�Once� an� overvoltage� condition� ends� the� ISL6566� continues�

�normal� operation� and� PGOOD� returns� high.�

�Pre-POR� Overvoltage� Protection�

�Prior� to� PVCC� and� VCC� exceeding� their� POR� levels,� the�

�ISL6566� is� designed� to� protect� the� load� from� any� overvoltage�

�events� that� may� occur.� This� is� accomplished� by� means� of� an�

�0.82� x� DAC�

�ISL6566� INTERNAL� CIRCUITRY�

�internal� 10k� ?� resistor� tied� from� PHASE� to� LGATE,� which�

�turns� on� the� lower� MOSFET� to� control� the� output� voltage�

�FIGURE� 13.� POWER� GOOD� AND� PROTECTION� CIRCUITRY�

�Power� Good� Signal�

�The� power� good� pin� (PGOOD)� is� an� open-drain� logic� output�

�that� transitions� high� when� the� converter� is� operating� after�

�soft-start.� PGOOD� pulls� low� during� shutdown� and� releases�

�high� after� a� successful� soft-start.� PGOOD� transitions� low�

�when� an� undervoltage,� overvoltage,� or� overcurrent� condition�

�is� detected� or� when� the� controller� is� disabled� by� a� reset� from�

�ENLL,� POR,� or� one� of� the� no-CPU� VID� codes.� If� after� an�

�undervoltage� or� overvoltage� event� occurs� the� output� returns�

�to� within� under� and� overvoltage� limits,� PGOOD� will� return�

�high.�

�19�

�until� the� overvoltage� event� ceases� or� the� input� power� supply�

�cuts� off.� For� complete� protection,� the� low� side� MOSFET�

�should� have� a� gate� threshold� well� below� the� maximum�

�voltage� rating� of� the� load/microprocessor.�

�In� the� event� that� during� normal� operation� the� PVCC� or� VCC�

�voltage� falls� back� below� the� POR� threshold,� the� pre-POR�

�overvoltage� protection� circuitry� reactivates� to� protect� from�

�any� more� pre-POR� overvoltage� events.�

�Open� Sense� Line� Protection�

�In� the� case� that� either� of� the� remote� sense� lines,� VSEN� or�

�GND,� become� open,� the� ISL6566� is� designed� to� detect� this�

�and� shut� down� the� controller.� This� event� is� detected� by�

�monitoring� the� voltage� on� the� IREF� pin,� which� is� a� local�

�version� of� V� OUT� sensed� at� the� outputs� of� the� inductors.�

�FN9178.4�

�March� 9,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| X5168S8I-2.7AT1 | IC SUPERVISOR CPU 16K EE 8-SOIC |

| ECC44DRES-S734 | CONN EDGECARD 88POS .100 EYELET |

| ISL6563CR-T | IC CTRLR PWM MULTIPHASE 24-QFN |

| ISL6563CR | IC CTRLR PWM MULTIPHASE 24-QFN |

| X5168S8I-2.7 | IC SUPERVISOR CPU 16K EE 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6566CRR5184 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Intersil Corporation 功能描述: |

| ISL6566CR-T | 功能描述:IC CTRLR PWM BUCK 3PHASE 40-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6566CRZ | 功能描述:IC CTRLR PWM BUCK 3PHASE 40QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6566CRZA | 制造商:Intersil Corporation 功能描述:CURRENT MODE PWM CNTRLR 0.8375V TO 1.6V 100A 40QFN EP - Rail/Tube |

| ISL6566CRZAR5184 | 功能描述:IC CTRLR PWM 3PHASE BUCK 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。