- 您现在的位置:买卖IC网 > PDF目录80362 > M32180F8TFP 32-BIT, FLASH, 80 MHz, RISC MICROCONTROLLER, PQFP240 PDF资料下载

参数资料

| 型号: | M32180F8TFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, FLASH, 80 MHz, RISC MICROCONTROLLER, PQFP240 |

| 封装: | 32 X 32 MM, 0.50 MM PITCH, PLASTIC, QFP-240 |

| 文件页数: | 26/139页 |

| 文件大小: | 3774K |

| 代理商: | M32180F8TFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页

5

5-10

INTERRUPT CONTROLLER (ICU)

32180 Group User’s Manual (Rev.1.0)

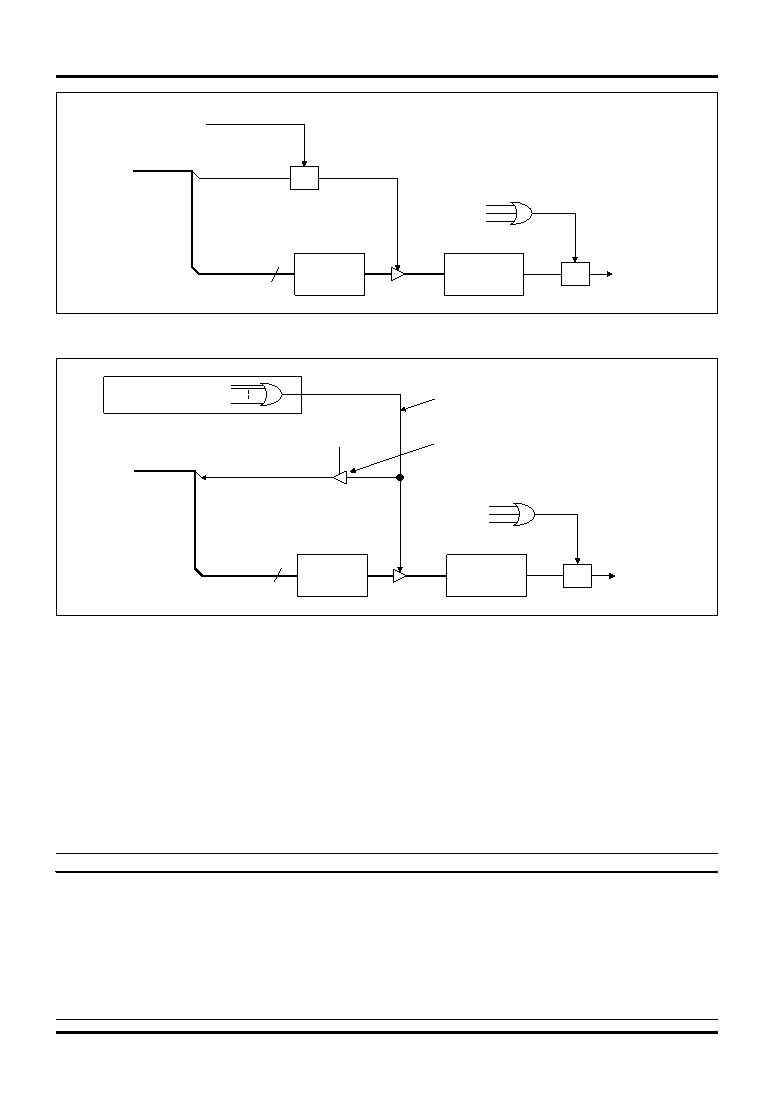

Figure 5.2.1 Configuration of the Interrupt Control Register (Edge-recognized Type)

5.2 ICU Related Registers

Figure 5.2.2 Configuration of the Interrupt Control Register (Level-recognized Type)

(2) ILEVEL (Interrupt Priority Level) (Bits 5–7 or bits 13–15)

These bits set the priority levels of interrupt requests from each internal peripheral I/O. Set these bits to ‘111’

to disable or any value ‘000’ through ‘110’ to enable the interrupt from some internal peripheral I/O.

When an interrupt occurs, the Interrupt Controller resolves priority between this interrupt and other interrupt

sources based on ILEVEL settings and finally compares priority with the IMASK value to determine whether

to forward an EI request to the CPU or keep the interrupt request pending.

The table below shows the relationship between ILEVEL settings and the IMASK values at which interrupts

are accepted.

Table 5.2.1 ILEVEL Settings and Accepted IMASK Values

ILEVEL values set

IMASK values at which interrupts are accepted

0 (ILEVEL = "000")

Accepted when IMASK is 1–7

1 (ILEVEL = "001")

Accepted when IMASK is 2–7

2 (ILEVEL = "010")

Accepted when IMASK is 3–7

3 (ILEVEL = "011")

Accepted when IMASK is 4–7

4 (ILEVEL = "100")

Accepted when IMASK is 5–7

5 (ILEVEL = "101")

Accepted when IMASK is 6–7

6 (ILEVEL = "110")

Accepted when IMASK is 7

7 (ILEVEL = "111")

Not accepted (interrupts disabled)

Interrupt request from

each internal peripheral I/O

Interrupt enabled

ILEVEL

(levels 0-7)

Data bus

Bits 5-7 or bits 13-15

3

F/F

Set

Set/clear

IREQ

Interrupt priority

resolving circuit

F/F

Reset

IVECT read

IMASK write

Clear

To the CPU core

Bit 3 or 11

Set

EI

Interrupt request from each

group internal peripheral I/O

Interrupt enabled

b3, b11

Data bus

b5-b7, b13-b15

Read

3

IREQ

Read-only circuit

ILEVEL

(levels 0-7)

Group interrupt

Interrupt priority

resolving circuit

F/F

Clear

To the CPU core

Set

EI

Reset

IVECT read

IMASK write

相关PDF资料 |

PDF描述 |

|---|---|

| M38002M2-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| M30623MAA-XXXGP | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| M37753M6C-XXXHP | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP80 |

| M38867E8A-XXXHP | 8-BIT, OTPROM, 5 MHz, MICROCONTROLLER, PQFP80 |

| M38867M8A-XXXHP | 8-BIT, MROM, 5 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M32180F8VFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:32-Bit RISC Single-Chip Microcomputers M32R Family M32R/ECU Series |

| M32180T2-PTC | 功能描述:DEV CONNECTION CNVTR FOR 32180 G RoHS:否 类别:编程器,开发系统 >> 配件 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program RoHS指令信息:IButton RoHS Compliance Plan 标准包装:1 系列:- 附件类型:USB 至 1-Wire? RJ11 适配器 适用于相关产品:1-Wire? 设备 产品目录页面:1429 (CN2011-ZH PDF) |

| M32182F3TFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:32-BIT RISC SINGLE-CHIP MICROCOMPUTER M32R FAMILY / M32R/ECU SERIES |

| M32182F3UFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:32-BIT RISC SINGLE-CHIP MICROCOMPUTER M32R FAMILY / M32R/ECU SERIES |

| M32182F3VFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:32-BIT RISC SINGLE-CHIP MICROCOMPUTER M32R FAMILY / M32R/ECU SERIES |

发布紧急采购,3分钟左右您将得到回复。