- 您现在的位置:买卖IC网 > PDF目录80464 > M38039GCHWG 8-BIT, MROM, 8.4 MHz, MICROCONTROLLER, PBGA64 PDF资料下载

参数资料

| 型号: | M38039GCHWG |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8.4 MHz, MICROCONTROLLER, PBGA64 |

| 封装: | 6 X 6 MM, 0.65 PITCH, FLGA-64 |

| 文件页数: | 25/103页 |

| 文件大小: | 1412K |

| 代理商: | M38039GCHWG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页

REJ03B0166-0113 Rev.1.13

Aug 21, 2009

Page 28 of 100

3803 Group (Spec.H QzROM version)

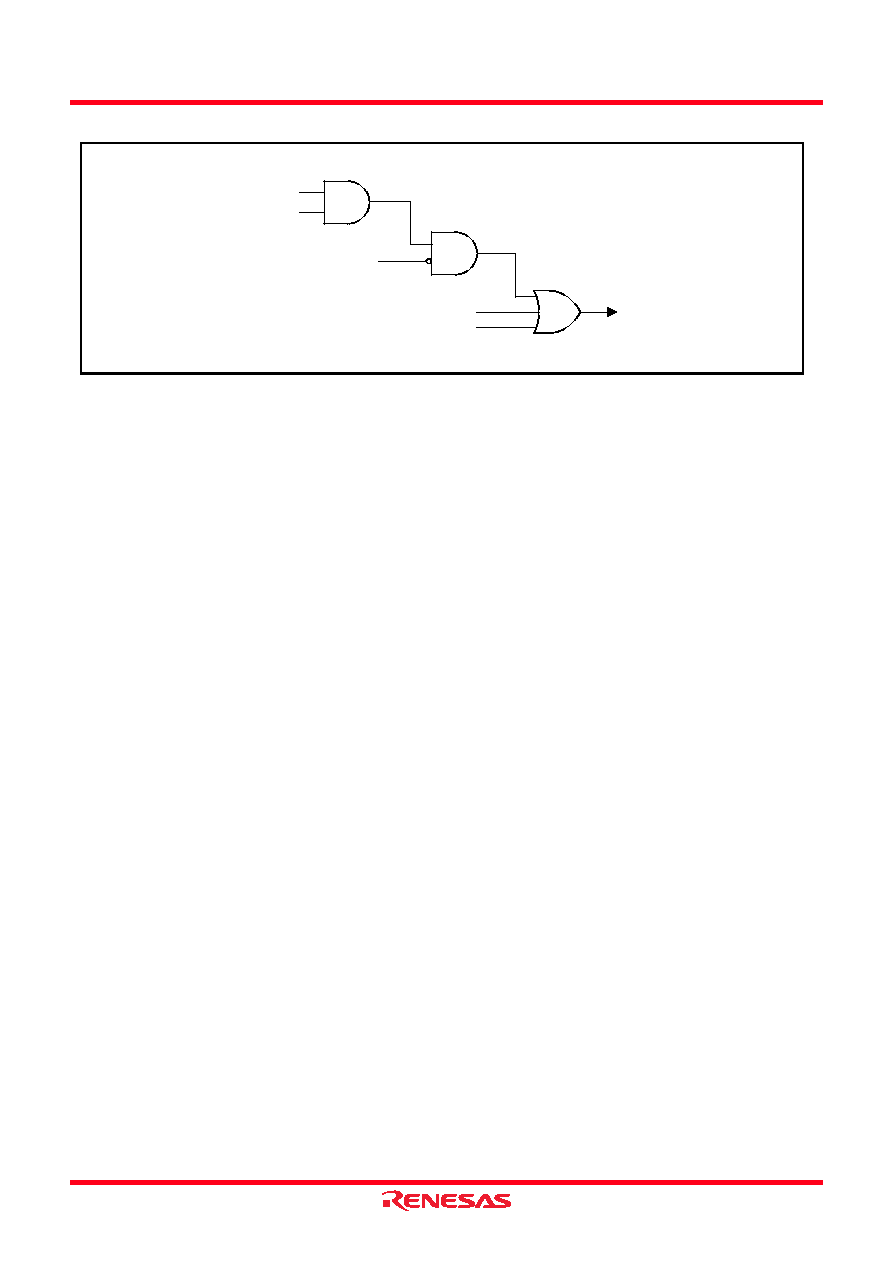

Fig 20. Interrupt control diagram

Interrupt Disable Flag

The interrupt disable flag is assigned to bit 2 of the processor

status register. This flag controls the acceptance of all interrupt

requests except for the BRK instruction. When this flag is set to

“1”, the acceptance of interrupt requests is disabled. When it is

set to “0”, acceptance of interrupt requests is enabled. This flag is

set to “1” with the SET instruction and set to “0” with the CLI

instruction.

When an interrupt request is accepted, the contents of the

processor status register are pushed onto the stack while the

interrupt disable flag remains set to “0”. Subsequently, this flag

is automatically set to “1” and multiple interrupts are disabled.

To use multiple interrupts, set this flag to “0” with the CLI

instruction within the interrupt processing routine.

The contents of the processor status register are popped off the

stack with the RTI instruction.

Interrupt Request Bits

Once an interrupt request is generated, the corresponding

interrupt request bit is set to “1” and remains “1” until the request

is accepted . Wh en the reques t is accepted, th is bit is

automatically set to “0”.

Each interrupt request bit can be set to “0”, but cannot be set to

“1”, by software.

Interrupt Enable Bits

The interrupt enable bits control the acceptance of the

corresponding interrupt requests. When an interrupt enable bit is

set to “0”, the acceptance of the corresponding interrupt request

is disabled. If an interrupt request occurs in this condition, the

corresponding interrupt request bit is set to “1”, but the interrupt

request is not accepted. When an interrupt enable bit is set to “1”,

acceptance of the corresponding interrupt request is enabled.

Each interrupt enable bit can be set to “0” or “1” by software.

The interrupt enable bit for an unused interrupt should be set to

“0”.

Interrupt Source Selection

Any of the following combinations can be selected by the

interrupt source selection register (003916).

1. INT0 or timer Z

2. CNTR1 or Serial I/O3 reception

3. Serial I/O2 or timer Z

4. INT4 or CNTR2

5. A/D conversion or serial I/O3 transmission

External Interrupt Pin Selection

For external interrupts INT0 and INT4, the INT0, INT4 interrupt

switch bit in the interrupt edge selection register (bit 6 of address

003A16) can be used to select INT00 and INT40 pin input or

INT01 and INT41 pin input.

Interrupt disable flag (I)

Interrupt request

Interrupt request bit

Interrupt enable bit

BRK instruction

Reset

相关PDF资料 |

PDF描述 |

|---|---|

| MSP430F2350IYFF | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PBGA49 |

| MK1707D | 108 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MPC8347ZUAGFA | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA672 |

| M30302GGPGP | 16-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQFP100 |

| MC3S12HN64J3CAA | 16-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M38049FFFP#U0 | 制造商:Renesas Electronics Corporation 功能描述: |

| M38049FFLHP#U0 | 制造商:Renesas Electronics Corporation 功能描述: |

| M38049RLSS | 功能描述:DEV EMULATOR CHIP RAM 2KB 64SDIP RoHS:否 类别:编程器,开发系统 >> 内电路编程器、仿真器以及调试器 系列:- 产品变化通告:Development Systems Discontinuation 19/Jul/2010 标准包装:1 系列:* 类型:* 适用于相关产品:* 所含物品:* |

| M3806 | 功能描述:电缆固定件和配件 LTSCG 625 BLACK RoHS:否 制造商:Heyco 类型:Cable Grips, Liquid Tight 材料:Nylon 颜色:Black 安装方法:Cable 最大光束直径:11.4 mm 抗拉强度: |

| M3806 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 8COND 18AWG BLK 1000' |

发布紧急采购,3分钟左右您将得到回复。