- 您现在的位置:买卖IC网 > PDF目录383305 > M5M5Y5672TG-20 (Mitsubishi Electric Corporation) 18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM PDF资料下载

参数资料

| 型号: | M5M5Y5672TG-20 |

| 厂商: | Mitsubishi Electric Corporation |

| 英文描述: | 18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| 中文描述: | 18874368位(262144 - Word的72位)网络的SRAM |

| 文件页数: | 13/27页 |

| 文件大小: | 240K |

| 代理商: | M5M5Y5672TG-20 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

MITSUBISHI LSIs

M5M5Y5672TG – 25,22,20

18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM

13

MITSUBISHI

ELECTRIC

Advanced Information

M5M5Y5672TG REV.0.1

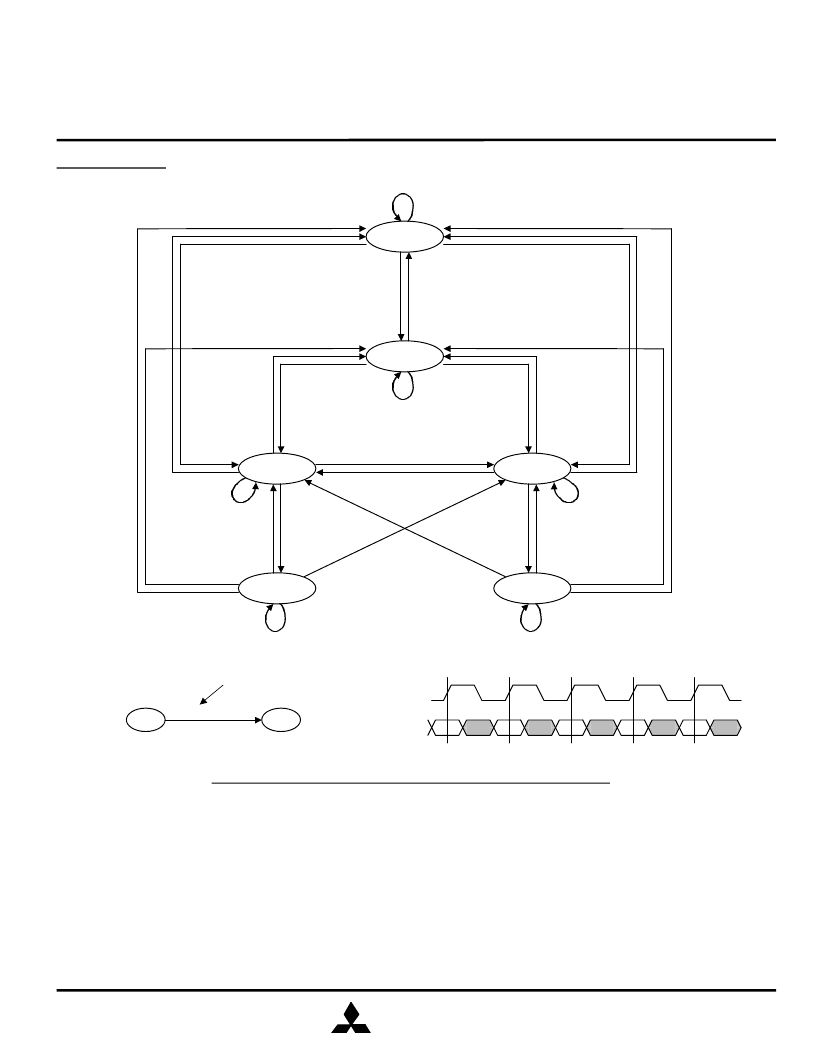

STATE DIAGRAM

Note21. The notation “X, X, X, X” controlling the state transitions above indicate the states of inputs E1#, E, ADV, and W# respectively.

Note22. If (E2=EP2 and E3=EP3) then E=”T” else E=”F”.

Note23. “H” = input “HIGH”; “L” = input “LOW”; “X” = input “don’t care”; “T” = input “true”; “F” = input “false”.

Bank

Deselect

Deselect

Write

Read

H, T, L, X or X, X, H, X

L, T, L, L

X, F, L, X

Write

Continue

X, F, L, X

L, T, L, L

X, X, H, X

X, X, H, X

H, T, L, X

H, T, L, X

H, T, L, X

X, F, L, X

L, T, L, H

L, T, L, L

Write

Continue

X, F, L, X

X, X, H, X

H, T, L, X

L, T, L, H

X, X, H, X

L, T, L, H

L, T, L, L

L, T, L, L

L, T, L, H

H, T, L, X

X, F, L, X

L, T, L, H

L, T, L, L

L, T, L, H

X, F, L, X or X, X, H, X

Current State (n)

Next State (n+1)

f

Transition

Input Command Code

Key

f

Current State

f

f

f

Next State

n

n+1

n+2

n+3

Clock

Command

Current State & Next State Definition for Read/Write Control State Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| M5M5Y5672TG-22 | 18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| M5M5Y5672TG-25 | 18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| M5M5Y816WG-70HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M5Y816WG-85HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M82C59AFP | The M5M82C59AFP,-2 is programmable LSI Interupt control |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5M80011A | 制造商:Mitsubishi Electric 功能描述: |

| M5M82C54P | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:CMOS PROGRAMMABLE INTERVAL TIMER |

| M5M82C54P-6 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:CMOS PROGRAMMABLE INTERVAL TIMER |

| M5M82C55AFP2 | 制造商:Panasonic Industrial Company 功能描述:IC |

| M5M82C59AFP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:The M5M82C59AFP,-2 is programmable LSI Interupt control |

发布紧急采购,3分钟左右您将得到回复。