- 您现在的位置:买卖IC网 > PDF目录359091 > M7020R-083ZA1T (意法半导体) 32K x 68-bit Entry NETWORK SEARCH ENGINE PDF资料下载

参数资料

| 型号: | M7020R-083ZA1T |

| 厂商: | 意法半导体 |

| 英文描述: | 32K x 68-bit Entry NETWORK SEARCH ENGINE |

| 中文描述: | 32K的× 68位进入网络搜索引擎 |

| 文件页数: | 73/150页 |

| 文件大小: | 996K |

| 代理商: | M7020R-083ZA1T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页当前第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页

73/150

M7020R

The following is the sequence of operation for a

single 136-bit SEARCH command (see COM-

MAND CODES AND PARAMETERS, page 29).

–

Cycle A:

The host ASIC drives the CMDV high

and applies SEARCH command code ('10') on

CMD[1:0] signals. CMD[5:3] signals must be

driven with the index to the GMR pair for use in

this SEARCH operation. CMD[8:7] signals must

be driven with the bits that will be driven on

SADR[21:20] by this device if it has a hit.

DQ[67:0] must be driven with the 68-bit data

([135:68]) in order to be compared against all

even locations. The CMD[2] signal must be driv-

en to logic '0.'

–

Cycle B:

The host ASIC continues to drive the

CMDV high and to apply SEARCH command

code ('10') on CMD[1:0]. CMD[5:2] must be driv-

en by the index of the comparand register pair

for storing the 136-bit word presented on the DQ

Bus during Cycles A and B. CMD[8:6] signals

must be driven with the index of the SSR that

will be used for storing the address of the

matching entry and the Hit Flag (see SEARCH-

Successful Registers (SSR[0:7]), page 23). The

DQ[67:0] is driven with 68-bit data ([67:0]) to be

compared against all odd locations.

The logical 136-bit SEARCH operation is as

shown in Figure 51, page 76. The entire table of 31

devices (consisting of 136-bit entries) is compared

against a 136-bit word K that is presented on the

DQ Bus in Cycles A and B of the command using

the GMR and local mask bits. The GMR is the 136-

bit word specified by the even and odd global

mask pair selected by the GMR Index in the com-

mand’s Cycle A.

The 136-bit word K that is presented on the DQ

Bus in Cycles A and B of the command is also

stored in the even and odd comparand registers

specified by the Comparand Register Index in the

command’s Cycle B. In x136 configurations, the

even and odd comparand registers can subse-

quently be used by the LEARN command in only

the first non-full device.

Note:

The LEARN command is supported for only

one of the blocks consisting of up to eight devices

in a depth-cascaded table of more than one block.

The word K that is presented on the DQ Bus in Cy-

cles A and B of the command is compared with

each entry in the table starting at location “0.” The

first matching entry’s location address, “L,” is the

winning address that is driven as part of the SRAM

address on the SADR[21:0] lines (see SRAM AD-

DRESSING, page 126). The global winning device

will drive the bus in a specific cycle. On global miss

cycles the device with LRAM = 1 (the default driv-

ing device for the SRAM bus) and LDEV = 1 (the

default driving device for SSF and SSV signals)

will be the default driver for such missed cycles.

Note:

During 136-bit searches of 136-bit-config-

ured tables, the search hit will always be at an

even address.

The SEARCH command is a pipelined operation.

It executes a search at half the rate of the frequen-

cy of CLK2X for 136-bit searches in x136-config-

ured tables. The latency of SADR, CE_L, ALE_L,

WE_L, SSV, and SSF from the 136-bit SEARCH

command cycle (two CLK2X cycles) is shown in

Table 39, page 88.

The latency of a search from command to the

SRAM access cycle is 6 for 1–31 devices in the ta-

ble and where TLSZ = 10. In addition, SSV and

SSF shift further to the right for different values of

HLAT, as specified in Table 40, page 88.

The 136-bit SEARCH operation is pipelined and

executes as follows:

– Four cycles from the SEARCH command, each

of the devices knows the outcome internal to it

for that operation.

– In the fifth cycle after the SEARCH command,

the devices in a block (being less than or equal

to eight devices resolving the winner within

them using the LHI[6:0] and LHO[1:0] signalling

mechanism) arbitrate for a winner amongst

them.

– In the sixth cycle after the SEARCH command,

the blocks (of devices) resolve the winning block

through the BHI[2:0] and BHO[2:0] signalling

mechanism. The winning device in the winning

block is the global winning device for a

SEARCH operation.

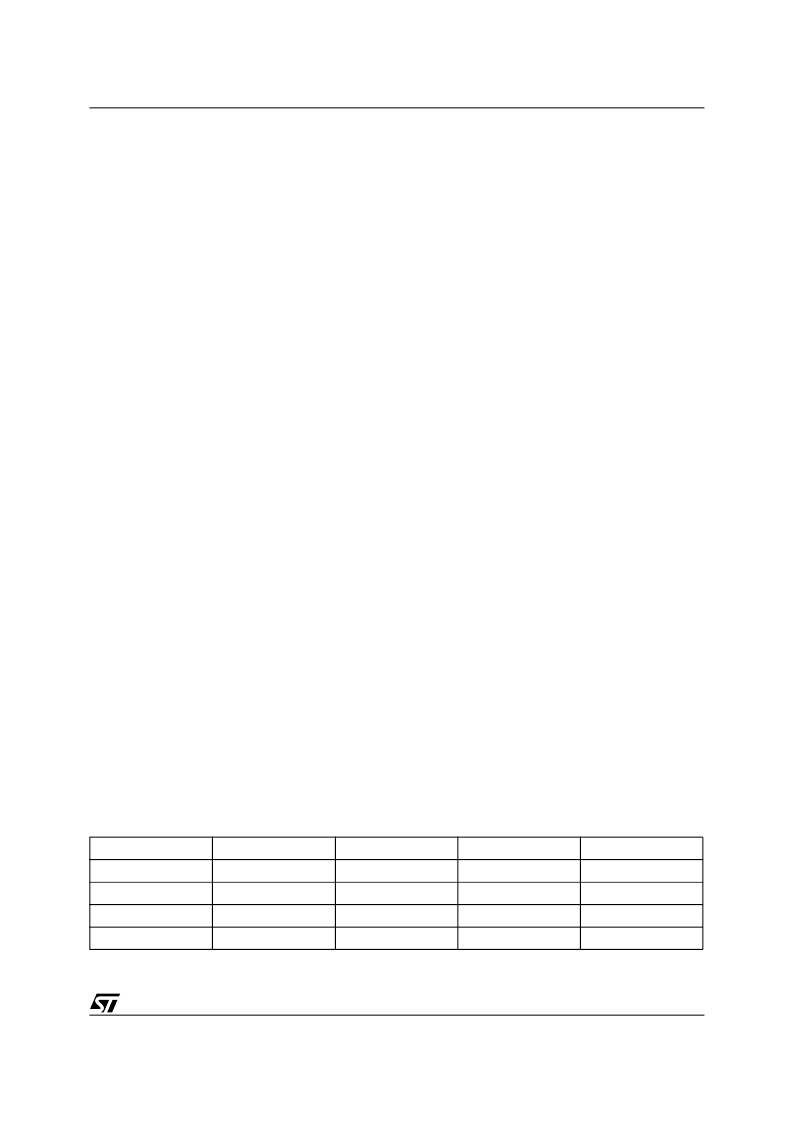

Table 38. Hit/Miss Assumption

Search Number

1

2

3

4

Block 0

Miss

Miss

Miss

Miss

Block 1

Miss

Miss

Hit

Miss

Block 2

Miss

Hit

Hit

Miss

Block 3

Hit

Hit

Miss

Miss

相关PDF资料 |

PDF描述 |

|---|---|

| M7020R | 32K x 68-bit Entry NETWORK SEARCH ENGINE |

| M72DW64000B | 64Mbit (x8/ x16, Multiple Bank, Boot Block) Flash Memory and 16Mbit Pseudo SRAM, 3V Supply, Multiple Memory Product |

| M72DW64000B70ZT | 64Mbit (x8/ x16, Multiple Bank, Boot Block) Flash Memory and 16Mbit Pseudo SRAM, 3V Supply, Multiple Memory Product |

| M72DW64000B90ZT | 64Mbit (x8/ x16, Multiple Bank, Boot Block) Flash Memory and 16Mbit Pseudo SRAM, 3V Supply, Multiple Memory Product |

| M74AC574TTR | OCTAL D-TYPE FLIP FLOP WITH 3 STATE OUTPUT NON INVERTING |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M702-230442 | 功能描述:火线接头 IEEE 1394 SMT 4P HORIZONTAL RoHS:否 制造商:Molex 产品:IEEE 1394 Firewire Connectors 标准:IEEE 1394 位置/触点数量:6 节距:2 mm 触点电镀:Unplated 触点材料:Phosphor Bronze 型式:Female 电流额定值:0.5 A 安装风格:Through Hole 端接类型:Solder Tab 连接器类型:Firewire Receptacle |

| M702-230642 | 功能描述:火线接头 IEEE 1394 SMT 6P HORIZONTAL RoHS:否 制造商:Molex 产品:IEEE 1394 Firewire Connectors 标准:IEEE 1394 位置/触点数量:6 节距:2 mm 触点电镀:Unplated 触点材料:Phosphor Bronze 型式:Female 电流额定值:0.5 A 安装风格:Through Hole 端接类型:Solder Tab 连接器类型:Firewire Receptacle |

| M7023 | 制造商:Tamura Corporation of America 功能描述: |

| M7027 | 功能描述:数字万用表 Dual Display Multime 0.3% Accuracy RoHS:否 制造商:Tektronix 产品:Multimeters 类型:Bench 准确性:0.04 % 电压范围:2 V to 2 kV 电阻范围: 电容范围: 显示计数: 频率:10 Hz to 45 Hz, 850 Hz to 1 MHz 测距: 真均方根值: 数据保持: |

| M7029 | 功能描述:数字万用表 Dual Display Multime 0.2% Accuracy RoHS:否 制造商:Tektronix 产品:Multimeters 类型:Bench 准确性:0.04 % 电压范围:2 V to 2 kV 电阻范围: 电容范围: 显示计数: 频率:10 Hz to 45 Hz, 850 Hz to 1 MHz 测距: 真均方根值: 数据保持: |

发布紧急采购,3分钟左右您将得到回复。