- 您现在的位置:买卖IC网 > PDF目录69018 > MB86860 (FUJITSU LTD) 32-BIT, 200 MHz, RISC PROCESSOR, PBGA352 PDF资料下载

参数资料

| 型号: | MB86860 |

| 厂商: | FUJITSU LTD |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA352 |

| 封装: | PLASTIC, BGA-352 |

| 文件页数: | 6/70页 |

| 文件大小: | 1395K |

| 代理商: | MB86860 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页

Specifications subject to changes without prior notice

15

MB86860 SPARClite

31

30

29

28

22

21

16

15

0

N

BW

Reserved

ASI<5:0>

Address<31:16>

Address: 0x80000100 (ASI=0x4)-0x8000128

Reset State: Undefined (ARSR0=0x80080000)

Figure 3-2 ARSR Register

bit31:

Non-cache [N]

bit30-29: Bus width [BW] (Reserved for CS#0)

bit29-22: Reserved

bit21-16: ASI<5:0> (Reserved for CS#0)

bit15-0:

Address<31:16> (Reserved for CS#0)

3.3. SDARS : SDRAM Address Range Specifier Register

This register is for setting SDRAM bus areas. Address ranges of starting addresses are set in this register. Bits

which do not make address comparisons are set in the SDAM Register. When N bit is 1, its range is set as a non-

cache area. All area settings must be set so as not to overlap. (CS0#~CS5# areas must also be set so as not to

overlap).

SDARS0 (0x80000130)

for setting SDRAM area

no corresponding CS# (Undefined on reset)

SDARS1 (0x80000138)

for setting SDRAM area

no corresponding CS# (Undefined on reset)

31

30

22

21

16

15

0

N

Reserved

ASI<5:0>

Address<31:16>

Address: 0x80000130 (ASI=0x4)-0x8000138

Reset State: Undefined

Figure 3-3 SDARS Register

bit31:

Non-cache [N]

bit30-22: Reserved

bit21-16: ASI<5:0>

bit15-0:

Address<31:16>

3.4. AMR : Address Mask Register

This is the register for setting CS0#~CS5# address ranges. It sets address ranges in combination with the ARSR

Register. Bits which are set 1 in the AMR Register do not compare addresses with the ARSR Register. Only AMR

Register bits set to 0 compare memory addresses with the ARSR Register and assert CS# if they agree. AMR and

CS# correspond as follows:

AMR0 (0x80000200)

for setting SPARC area

CS0#

(ROM area exclusive use. 0x00030001 on reset)

AMR1 (0x80000208)

for setting SPARC area

CS1#

(Undefined on reset)

AMR2 (0x80000210)

for setting SPARC area

CS2#

(Undefined on reset)

AMR3 (0x80000218)

for setting SPARC area

CS3#

(Undefined on reset)

AMR4 (0x80000220)

for setting SPARC area

CS4#

(Undefined on reset)

AMR5 (0x80000228)

for setting SPARC area

CS5#

(Undefined on reset)

31

22

21

16

15

0

Reserved

ASI mask<5:0>

Address mask<31:16>

Address: 0x80000200 (ASI=0x4)-0x8000228

Reset State: Undefined (AMR0=0x00030001)

Figure 3-4 AMR Register

bit31-22: Reserved

bit21-16: ASI<5:0>

bit15-0:

Address<31:16>

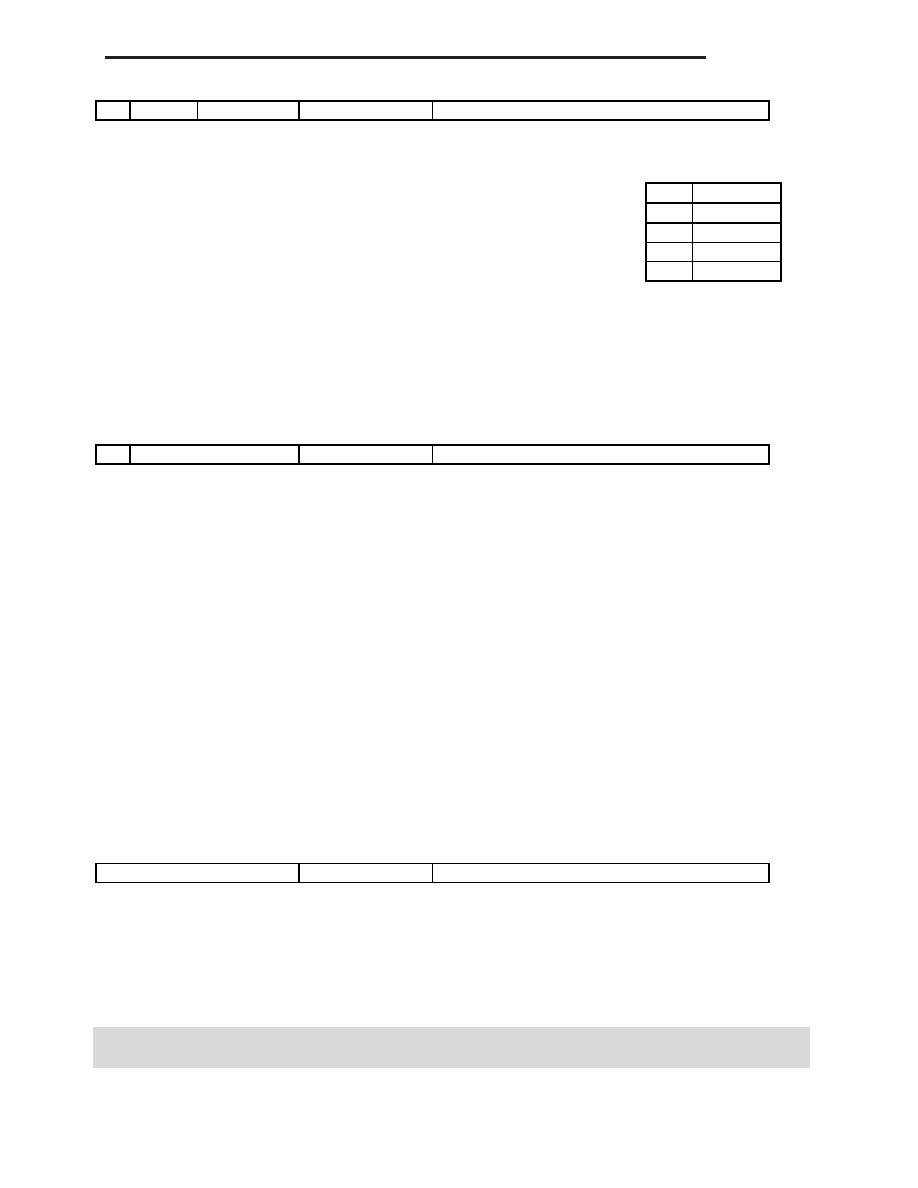

BW

Bus width

00

64 bit

01

32 bit

10

16 bit

11

8 bit

Table 3-4 Bus

width

相关PDF资料 |

PDF描述 |

|---|---|

| MB86931-20ZF-G | 32-BIT, 20 MHz, RISC MICROCONTROLLER, CQFP256 |

| MB86931-40ZF-G | 32-BIT, 40 MHz, RISC MICROCONTROLLER, CQFP256 |

| MB86933H-20PF-G | 32-BIT, 20 MHz, RISC PROCESSOR, PQFP160 |

| MB86934-60ZF | 32-BIT, 60 MHz, RISC PROCESSOR, CQFP256 |

| MB86936-25/50-PFV-G | 32-BIT, 25 MHz, RISC PROCESSOR, PQFP208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB86930-30ZF-G-BND | 制造商:FUJITSU 功能描述: |

| MB86941 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86941PFV | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86942 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86942PFV | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

发布紧急采购,3分钟左右您将得到回复。