- 您现在的位置:买卖IC网 > PDF目录69018 > MB86860 (FUJITSU LTD) 32-BIT, 200 MHz, RISC PROCESSOR, PBGA352 PDF资料下载

参数资料

| 型号: | MB86860 |

| 厂商: | FUJITSU LTD |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA352 |

| 封装: | PLASTIC, BGA-352 |

| 文件页数: | 7/70页 |

| 文件大小: | 1395K |

| 代理商: | MB86860 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页

Specifications subject to changes without prior notice

16

MB86860 SPARClite

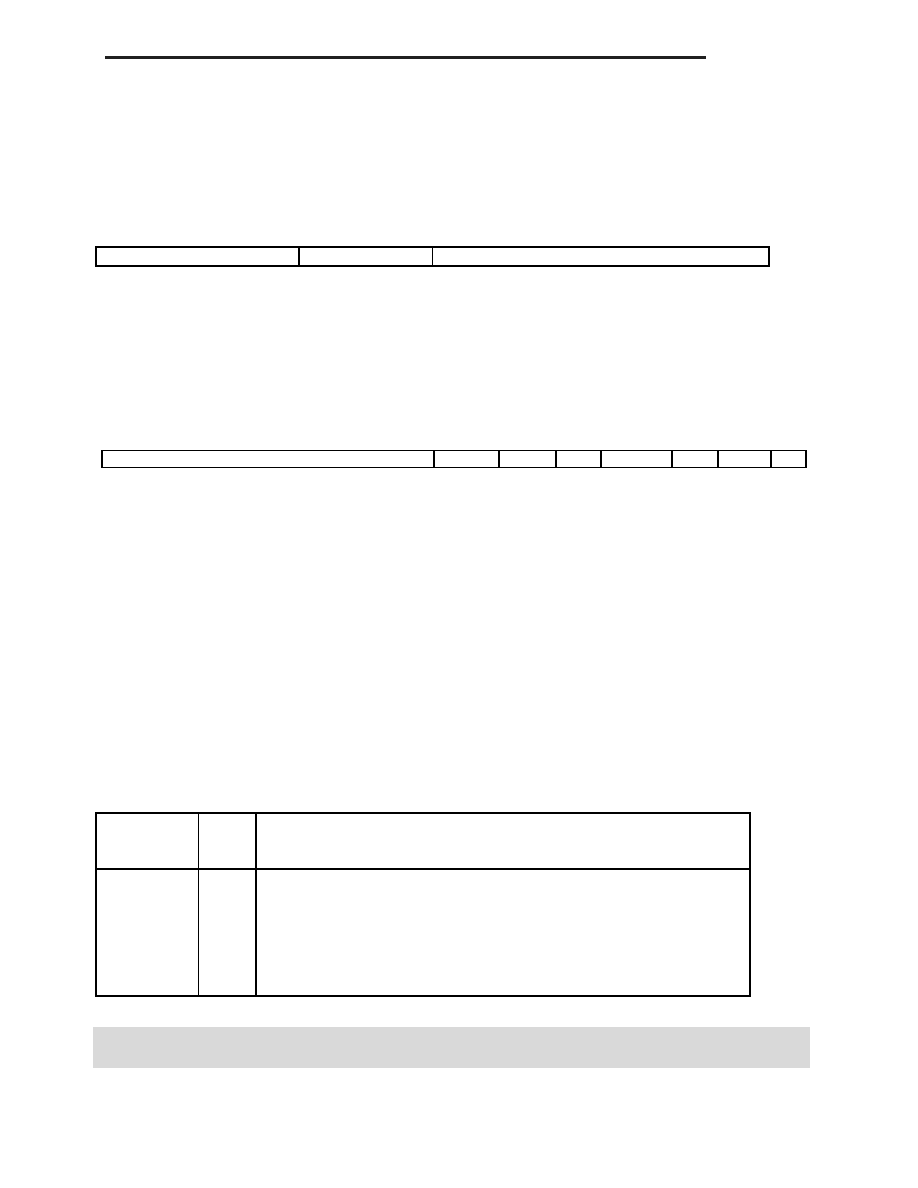

3.5. SDAM : SDRAM Address Mask Register

This register is for setting SDRAM address ranges. It sets address ranges in combination with the SDARS Register.

Bits which are set 1 in the AMR Register do not compare addresses with the SDARS Register. Only SDAM Register

bits set to 0 compare memory addresses with the SDARS Register, and if they agree regard this as access to SDRAM.

SDAMR0 (0x80000230)

for setting SDRAM area no corresponding CS# (Undefined on reset)

SDAMR1 (0x80000238)

for setting SDRAM area no corresponding CS# (Undefined on reset)

31

22

21

16

15

0

Reserved

ASI mask<5:0>

Address mask<31:16>

Address: 0x80000230 (ASI=0x4)-0x8000238

Reset State: Undefined

Figure 3-5 SDAM Register

bit31-22: Reserved

bit21-16: ASI<5:0>

bit15-0:

Address<31:16>

3.6. WSSR : Wait State Specifier Register

Sets wait state generation for all CS# areas.

31

15

14

10

9

5

4

3

2

1

0

Reserved

CN1

CN2

WE

Reserved

OVR

SCB

PE

Address: 0x80000400 (ASI=0x4):

CS0#

Reset State: 0x00007ff4

Address: 0x80000408 (ASI=0x4):

CS1#

Reset State: 0x00000000

Address: 0x80000410 (ASI=0x4):

CS2#

Reset State: 0x00000000

Address: 0x80000418 (ASI=0x4):

CS3#

Reset State: 0x00000000

Address: 0x80000420 (ASI=0x4):

CS4#

Reset State: 0x00000000

Address: 0x80000428 (ASI=0x4):

CS5#

Reset State: 0x00000000

Figure 3-6 WSSR Register

bit31-15: Reserved

bit14-10: count1 [CN1]

bit9-5:

count2 [CN2]

bit4:

wait enable [WE]

bit3:

Reserved

bit2:

override [OVR

bit1:

single cycle burst mode [SCB]

bit0:

parity enable [PE]

Table 3-5

wait enable

[WE]

Enables internal wait state generation for corresponding CS areas.

[OVR], [CN1], [CN2] and [SCB] functions all become valid when [WE] is

“1”.

override

[OVR]

When this bit is “1”, external READY# is also received. (The READY#

which comes first is given priority), When this bit is “0”, READY# from

the exterior is masked and received. However, the mask function does

not work for READY# which is input in the same cycle as AS#, in other

words for READY# which is input by 0wait.

This bit becomes valid when [WE] is “1”.

Thus this bit should be set

together with [WE].

相关PDF资料 |

PDF描述 |

|---|---|

| MB86931-20ZF-G | 32-BIT, 20 MHz, RISC MICROCONTROLLER, CQFP256 |

| MB86931-40ZF-G | 32-BIT, 40 MHz, RISC MICROCONTROLLER, CQFP256 |

| MB86933H-20PF-G | 32-BIT, 20 MHz, RISC PROCESSOR, PQFP160 |

| MB86934-60ZF | 32-BIT, 60 MHz, RISC PROCESSOR, CQFP256 |

| MB86936-25/50-PFV-G | 32-BIT, 25 MHz, RISC PROCESSOR, PQFP208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB86930-30ZF-G-BND | 制造商:FUJITSU 功能描述: |

| MB86941 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86941PFV | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86942 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86942PFV | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

发布紧急采购,3分钟左右您将得到回复。