- 您现在的位置:买卖IC网 > PDF目录69025 > MC68CK338CPV14B1 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 14.4 MHz, MICROCONTROLLER, PQFP144 PDF资料下载

参数资料

| 型号: | MC68CK338CPV14B1 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 14.4 MHz, MICROCONTROLLER, PQFP144 |

| 封装: | PLASTIC, TQFP-144 |

| 文件页数: | 55/133页 |

| 文件大小: | 944K |

| 代理商: | MC68CK338CPV14B1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页当前第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页

MOTOROLA

MC68CK338

28

MC68CK338TS/D

3.5.6 Data Strobe

Data strobe (DS) is a timing signal. For a read cycle, the MCU asserts DS to signal an external device

to place data on the bus. DS is asserted at the same time as AS during a read cycle. For a write cycle,

DS signals an external device that data on the bus is valid. The MCU asserts DS one full clock cycle

after the assertion of AS during a write cycle.

3.5.7 Bus Cycle Termination Signals

During bus cycles, external devices assert the data size acknowledge signals DSACK1 and DSACK0.

During a read cycle, the signals tell the MCU to terminate the bus cycle and to latch data. During a write

cycle, the signals indicate that an external device has successfully stored data and that the cycle can

end. These signals also indicate to the MCU the size of the port for the bus cycle just completed. Alter-

nately, chip-selects can be used to generate DSACK1 and DSACK0 internally. Refer to 3.5.8 Dynamic

Bus Sizing for more information.

The bus error (BERR) signal is also a bus cycle termination indicator and can be used in the absence

of DSACK1 and DSACK0 to indicate a bus error condition. It can also be asserted in conjunction with

these signals, provided it meets the appropriate timing requirements. The internal bus monitor can be

used to generate the BERR signal for internal-to-external transfers. When BERR and HALT are assert-

ed simultaneously, the CPU takes a bus error exception.

The autovector signal (AVEC) can terminate IRQ pin interrupt acknowledge cycles. AVEC indicates that

the MCU will internally generate a vector number to locate an interrupt handler routine. If it is continu-

ously asserted, autovectors will be generated for all external interrupt requests. AVEC is ignored during

all other bus cycles.

3.5.8 Dynamic Bus Sizing

The MCU dynamically interprets the port size of the addressed device during each bus cycle, allowing

operand transfers to or from 8- and 16-bit ports. During an operand transfer cycle, the slave device sig-

nals its port size and indicates completion of the bus cycle to the MCU through the use of the DSACK1

and DSACK0 inputs, as shown in Table 15.

For example, if the MCU is executing an instruction that reads a long-word operand from a 16-bit port,

the MCU latches the 16 bits of valid data and then runs another bus cycle to obtain the other 16 bits.

The operation for an 8-bit port is similar, but requires four read cycles. The addressed device uses the

DSACK0 and DSACK1 signals to indicate the port width. For instance, a 16-bit device always returns

DSACK0 = 1 and DSACK1 = 0 for a 16-bit port, regardless of whether the bus cycle is a byte or word

operation.

Dynamic bus sizing requires that the portion of the data bus used for a transfer to or from a particular

port size be fixed. A 16-bit port must reside on data bus bits [15:0] and an 8-bit port must reside on data

bus bits [15:8]. This minimizes the number of bus cycles needed to transfer data and ensures that the

MCU transfers valid data.

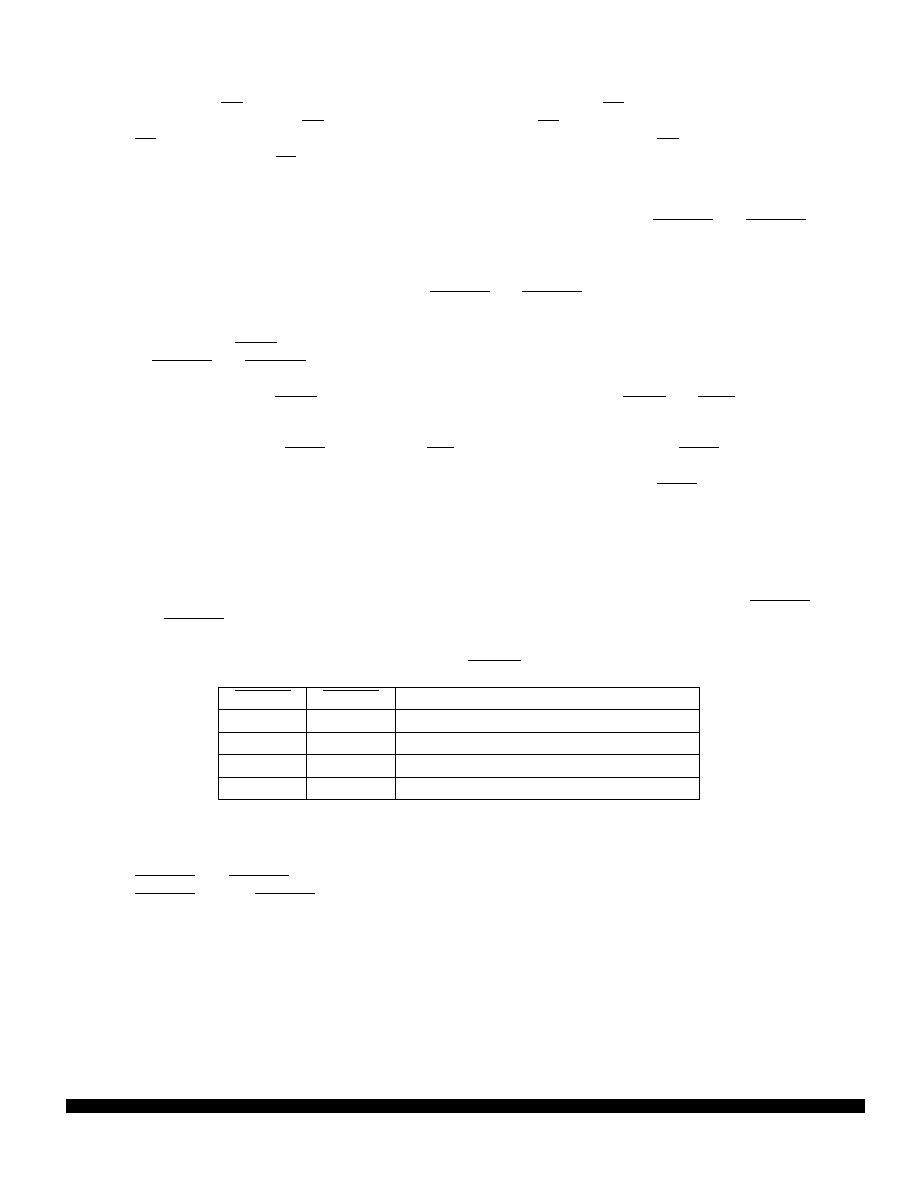

Table 15 Effect of DSACK Signals

DSACK1

DSACK0

Result

1

Insert Wait States in Current Bus Cycle

1

0

Complete Cycle — Data Bus Port Size is 8 Bits

0

1

Complete Cycle — Data Bus Port Size is 16 Bits

0

Reserved

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相关PDF资料 |

PDF描述 |

|---|---|

| MC68CK338CPV14 | 32-BIT, 14.4 MHz, MICROCONTROLLER, PQFP144 |

| MC68EN360CRC25 | 32-BIT, 25 MHz, RISC MICROCONTROLLER, CPGA241 |

| MC68F333FE | 32-BIT, FLASH, 16.78 MHz, MICROCONTROLLER, CQFP160 |

| MC68F333FC | 32-BIT, FLASH, 16.78 MHz, MICROCONTROLLER, PQFP160 |

| MC68HC000L12F | 16-BIT, 16.67 MHz, MICROPROCESSOR, CDIP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC68CM16Z1 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

| MC68CM16Z1CFC16 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

| MC68CM16Z1CPV16 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series |

| MC68E360VR25VLR2 | 功能描述:微处理器 - MPU QUICC ETHRN RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MC68E360ZP25VLR2 | 功能描述:IC MPU QUICC 32BIT 357-PBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:M683xx 标准包装:1 系列:MPC85xx 处理器类型:32-位 MPC85xx PowerQUICC III 特点:- 速度:1.2GHz 电压:1.1V 安装类型:表面贴装 封装/外壳:783-BBGA,FCBGA 供应商设备封装:783-FCPBGA(29x29) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。