- 您现在的位置:买卖IC网 > PDF目录69034 > ML60851EGA (OKI ELECTRIC INDUSTRY CO LTD) UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | ML60851EGA |

| 厂商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| 封装: | 0.80 MM PITCH, PLASTIC, QFP-44 |

| 文件页数: | 65/88页 |

| 文件大小: | 1137K |

| 代理商: | ML60851EGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页当前第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

Oki Semiconductor

ML60851E

66/84

Interrupts

The ML60851E requests interrupts to the local MCU, etc., by asserting the -INTR pin. The interrupt causes are the

following:

(a)

Setup ready for the 8-byte setup data

(b)

EP0 receive packet ready

(c)

EP0 transmit packet ready

(d)

EP1 transmit/receive packet ready

(e)

EP2 transmit/receive packet ready

(f)

EP3 transmit packet ready

(g)

USB Bus reset

(h)

Suspend

Although there is only one

INTR pin, the local MCU can identify the contents of the interrupt by reading out the

interrupt status register. These interrupts can also be masked dynamically by making individual settings in the

interrupt enable register.

The causes of the interrupts, their setting and resetting conditions, and the responses to them are described below.

The functions of the setup ready bit and the packet ready bit can, in some situations, be different from those

described here because of some special automatic operations done by the ML60851E. Please see the descriptions

of the registers EP0STAT and PKTRDY for more details of such functions.

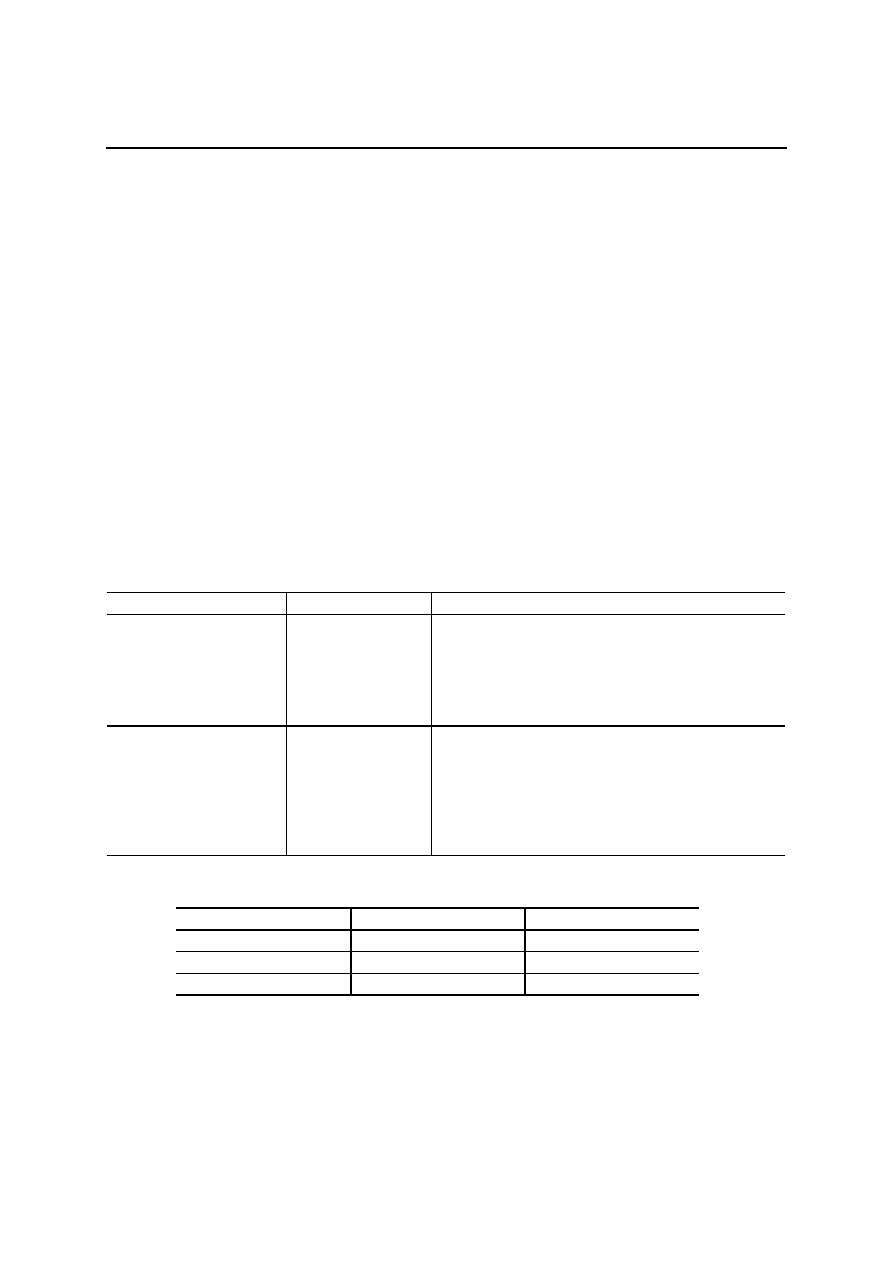

(1) Setup ready interrupt

Operation

Source of operation

Description (conditions, responses, etc.)

Setup ready

interrupt generation

ML60851E

The setup ready bit (D0 of EP0STAT) is asserted when the

8-byte setup control data is received normally and has

been stored in the set of setup registers.

An interrupt is generated at this time if D0 of INTENBL has

been asserted.

→ The firmware can now read the set of setup registers.

End of setup ready interrupt Local MCU (firmware)

After making the firmware read the 8-byte setup data, write

a “1” in bit D0 of EP0 status register (EP0STAT). This

causes the interrupt to be de-asserted.

The interrupt will not be de-asserted If a new 8-byte setup

data is received during this period. In this case, discard the

setup data that was being read at that time and read the

new 8-byte setup data.

The following table outlines the relationship between ML60851E registers and setup ready interrupt generation.

INTENBL(D0)

EP0STAT(D0)

INTSTAT(D0)

1

0

1

0

X

0

X This symbol means that it does not matter whether the value is ‘1’ or ‘0’

相关PDF资料 |

PDF描述 |

|---|---|

| ML60851ETB | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML610Q346 | RISC MICROCONTROLLER, PQFP64 |

| ML610346 | RISC MICROCONTROLLER, PQFP64 |

| ML610Q347J-NNNTB | 8-BIT, FLASH, 4.2 MHz, RISC MICROCONTROLLER, PQFP64 |

| ML610347-XXXTB | 8-BIT, MROM, 4.2 MHz, RISC MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ML60851ETB | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60852 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60852A | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60852ATBZ010 | 功能描述:USB 接口集成电路 12 Mbps; USB Device Controller RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

| ML60852ATBZ03A | 制造商:ROHM Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。