- 您现在的位置:买卖IC网 > PDF目录29137 > MPC9893FAR2 (INTEGRATED DEVICE TECHNOLOGY INC) 9893 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 PDF资料下载

参数资料

| 型号: | MPC9893FAR2 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 9893 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| 封装: | 7 X 7 MM, LQFP-48 |

| 文件页数: | 15/16页 |

| 文件大小: | 285K |

| 代理商: | MPC9893FAR2 |

MPC9893

MOTOROLA

TIMING SOLUTIONS

8

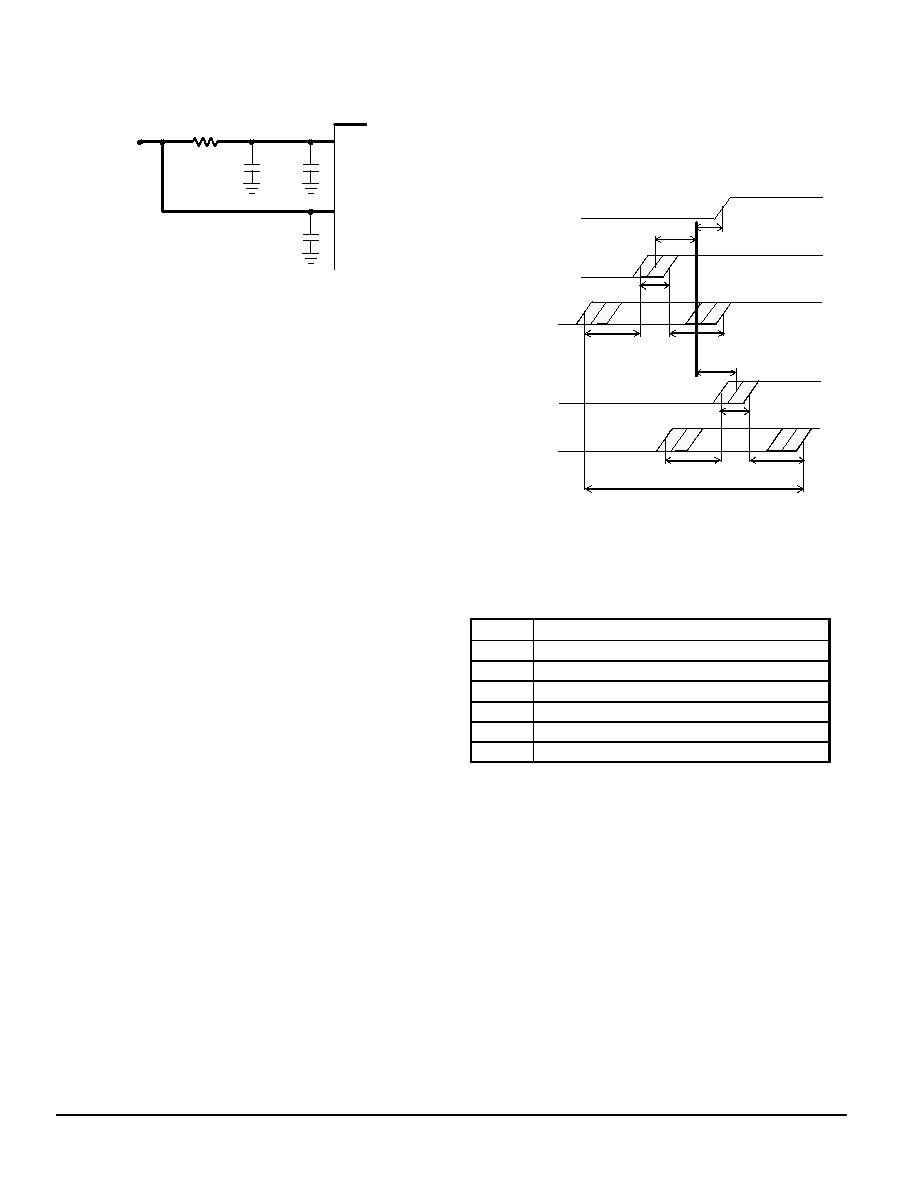

Figure 3. VCC_PLL Power Supply Filter

VCC_PLL

VCC

MPC9893

10 nF

RF =9--10

CF

33...100 nF

RF

VCC

CF =22 F

The minimum values for RF and the filter capacitor CF are

defined by the required filter characteristics: the RC filter

should provide an attenuation greater than 40 dB for noise

whose spectral content is above 100 kHz. In the example RC

filter shown in Figure 3. “VCC_PLL Power Supply Filter”, the

filter cut-off frequency is around 3-5 kHz and the noise

attenuation at 100 kHz is better than 42 dB.

As the noise frequency crosses the series resonant point

of an individual capacitor its overall impedance begins to look

inductive and thus increases with increasing frequency. The

parallel capacitor combination shown ensures that a low

impedance path to ground exists for frequencies well above

the bandwidth of the PLL. Although the MPC9893 has

several design features to minimize the susceptibility to

power supply noise (isolated power and grounds and fully

differential PLL) there still may be applications in which

overall performance is being degraded due to system power

supply noise. The power supply filter schemes discussed in

this section should be adequate to eliminate power supply

noise related problems in most designs.

Using the MPC9893 in zero--delay applications

Nested clock trees are typical applications for the

MPC9893. Designs using the MPC9893 as LVCMOS PLL

fanout buffer with zero insertion delay will show significantly

lower clock skew than clock distributions developed from

CMOS fanout buffers. The external feedback option of the

MPC9893 clock driver allows for its use as a zero delay

buffer. The the propagation delay through the device is

virtually eliminated. The PLL aligns the feedback clock output

edge with the clock input reference edge resulting a near zero

delay through the device. The maximum insertion delay of

the device in zero--delay applications is measured between

the reference clock input and any output. This effective delay

consists of the static phase offset, I/O jitter (phase or

long -- term jitter), feedback path delay and the

output--to--output skew error relative to the feedback output.

Calculation of part-to-part skew

The MPC9893 zero delay buffer supports applications

where critical clock signal timing can be maintained across

several devices. If the reference clock inputs of two or more

MPC9893 are connected together, the maximum overall

timing uncertainty from the common CLK0 or CLK1 input to

any output is:

This maximum timing uncertainty consist of 4

components: static phase offset, output skew, feedback

board trace delay and I/O (phase) jitter:

tSK PP

()

t

()

tSK O

()

tPD LINE FB

()

,

tJIT

() CF

×

++

+

=

CLKx

Common

QFB

Device 1

Any Q

Device 1

QFB

Device2

Any Q

Device 2

Max. skew

t

PD,LINE(FB)

t

JIT()

±t

SK(O)

–t

()

+t

()

t

JIT()

±t

SK(O)

t

SK(PP)

Figure 4. Max. I/O Jitter versus frequency

Due to the statistical nature of I/O jitter a rms value (1 σ)is

specified. I/O jitter numbers for other confidence factors (CF)

can be derived from Table 10.

Table 10: Confidence Facter CF

CF

Probability of clock edge within the distribution

± 1σ

0.68268948

± 2σ

0.95449988

± 3σ

0.99730007

± 4σ

0.99993663

± 5σ

0.99999943

± 6σ

0.99999999

The feedback trace delay is determined by the board

layout and can be used to fine-tune the effective delay

through each device. In the following example calculation a

I/O jitter confidence factor of 99.7% (± 3σ) is assumed,

resulting in a worst case timing uncertainty from the common

clock input to any MPC9893 output of -275 ps to +265 ps

relative to the reference clock input CLK0/1:

tSK(PP) =

[--60ps...50ps] + [--125ps...125ps] +

[(30ps --3)...(30ps 3)] + tPD, LINE(FB)

tSK(PP) =

[--275ps...265ps] + tPD, LINE(FB)

Example configuration: fref=100 MHz, VCC=3.3V

fVCO=400 MHz, FSEL[0:2]=111

The I/O (Phase) jitter of the MPC9893 depends on the

internal VCO frequency and the PLL feedback divider

configuration. A high internal VCO frequency and a low PLL

相关PDF资料 |

PDF描述 |

|---|---|

| MPC991FAR2 | PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC991FAR2 | PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC993FA | 993 SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| MPC9952FAR2 | PLL BASED CLOCK DRIVER, 11 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| MPC9952FA | PLL BASED CLOCK DRIVER, 11 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9894 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Quad Input Redundant IDCS Clock Generator |

| MPC9894VM | 制造商:IDT from Components Direct 功能描述:IDT MPC9894VM PLL - Trays 制造商:IDT 功能描述:IDT MPC9894VM PLL |

| MPC990 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC990F18 F44A WAF | 制造商:Motorola Inc 功能描述: |

| MPC991 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

发布紧急采购,3分钟左右您将得到回复。