- 您现在的位置:买卖IC网 > PDF目录19294 > MSC8126TVT6400 (Freescale Semiconductor)IC DSP QUAD 16B 400MHZ 431FCPBGA PDF资料下载

参数资料

| 型号: | MSC8126TVT6400 |

| 厂商: | Freescale Semiconductor |

| 文件页数: | 23/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP QUAD 16B 400MHZ 431FCPBGA |

| 标准包装: | 60 |

| 系列: | StarCore |

| 类型: | SC140 内核 |

| 接口: | DSI,以太网,RS-232 |

| 时钟速率: | 400MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 1.436MB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 431-BFBGA,FCBGA |

| 供应商设备封装: | 431-FCPBGA(20x20) |

| 包装: | 托盘 |

| 配用: | MSC8126ADSE-ND - KIT ADVANCED DEV SYSTEM 8126 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

�� �

�

Electrical� Characteristics�

�The� UPM� machine� and� GPCM� machine� outputs� change� on� the� internal� tick� selected� by� the� memory� controller� configuration.�

�The� AC� timing� specifications� are� relative� to� the� internal� tick.� SDRAM� machine� outputs� change� only� on� the� REFCLK� rising� edge.�

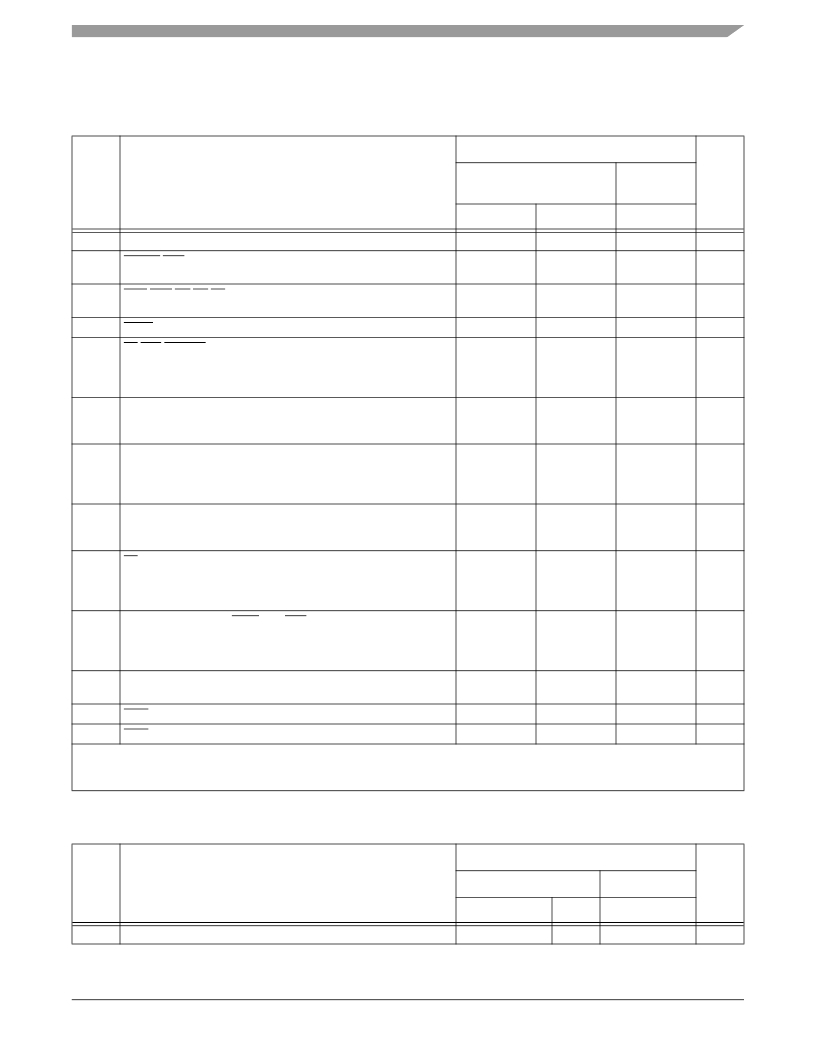

�Table� 14.� AC� Timing� for� SIU� Inputs�

�Value� for� Bus� Speed� in� MHz�

�No.�

�Characteristic�

�Ref� =� CLKIN�

�133�

�166�

�Ref� =�

�CLKOUT�

�133�

�Units�

�10�

�11a�

�Hold� time� for� all� signals� after� the� 50%� level� of� the� REFCLK� rising� edge�

�ARTRY/ABB� set-up� time� before� the� 50%� level� of� the� REFCLK� rising�

�0.5�

�3.0�

�0.5�

�3.0�

�0.5�

�3.0�

�ns�

�ns�

�edge�

�11b�

�DBG/DBB/BG/BR/TC� set-up� time� before� the� 50%� level� of� the�

�3.3�

�3.3�

�3.3�

�ns�

�REFCLK� rising� edge�

�11c�

�AACK� set-up� time� before� the� 50%� level� of� the� REFCLK� rising� edge�

�2.9�

�2.9�

�2.9�

�ns�

�11d�

�TA/TEA/PSDVAL� set-up� time� before� the� 50%� level� of� the� REFCLK�

�rising� edge�

�?� Data-pipeline� mode�

�?� Non-pipeline� mode�

�3.4�

�4.0�

�3.4�

�4.0�

�3.4�

�4.0�

�ns�

�ns�

�12�

�Data� bus� set-up� time� before� REFCLK� rising� edge� in� Normal� mode�

�?� Data-pipeline� mode�

�?� Non-pipeline� mode�

�1.8�

�4.0�

�1.7�

�4.0�

�1.8�

�4.0�

�ns�

�ns�

�13� 1�

�Data� bus� set-up� time� before� the� 50%� level� of� the� REFCLK� rising� edge�

�in� ECC� and� PARITY� modes�

�?� Data-pipeline� mode�

�?� Non-pipeline� mode�

�2.0�

�7.3�

�2.0�

�7.3�

�2.0�

�7.3�

�ns�

�ns�

�14� 1�

�DP� set-up� time� before� the� 50%� level� of� the� REFCLK� rising� edge�

�?� Data-pipeline� mode�

�?� Non-pipeline� mode�

�2.0�

�6.1�

�2.0�

�6.1�

�2.0�

�6.1�

�ns�

�ns�

�15a�

�TS� and� Address� bus� set-up� time� before� the� 50%� level� of� the� REFCLK�

�rising� edge�

�?� Extra� cycle� mode� (SIUBCR[EXDD]� =� 0)�

�?� No� extra� cycle� mode� (SIUBCR[EXDD]� =� 1)�

�3.6�

�5.0�

�3.6�

�5.0�

�3.8�

�5.0�

�ns�

�ns�

�15b�

�Address� attributes:� TT/TBST/TSZ/GBL� set-up� time� before� the� 50%�

�level� of� the� REFCLK� rising� edge�

�?� Extra� cycle� mode� (SIUBCR[EXDD]� =� 0)�

�?� No� extra� cycle� mode� (SIUBCR[EXDD]� =� 1)�

�3.5�

�4.4�

�3.5�

�4.4�

�3.5�

�4.4�

�ns�

�ns�

�16�

�PUPMWAIT� signal� set-up� time� before� the� 50%� level� of� the� REFCLK�

�3.7�

�3.7�

�3.7�

�ns�

�rising� edge�

�17�

�IRQx� setup� time� before� the� 50%� level;� of� the� REFCLK� rising� edge� 3�

�4.0�

�4.0�

�4.0�

�ns�

�18�

�IRQx� minimum� pulse�

�width� 3�

�6.0� +� T� REFCLK�

�6.0� +� T� REFCLK�

�6.0� +� T� REFCLK�

�ns�

�Notes:�

�1.�

�2.�

�3.�

�Timings� specifications� 13� and� 14� in� non-pipeline� mode� are� more� restrictive� than� MSC8102� timings.�

�Values� are� measured� from� the� 50%� TTL� transition� level� relative� to� the� 50%� level� of� the� REFCLK� rising� edge.�

�Guaranteed� by� design�

�Table� 15.� AC� Timing� for� SIU� Outputs�

�Value� for� Bus� Speed� in� MHz�

�No.�

�Characteristic�

�Ref� =� CLKIN�

�133�

�166�

�Ref� =� CLKOUT�

�133�

�Units�

�30� 2�

�Minimum� delay� from� the� 50%� level� of� the� REFCLK� for� all� signals�

�0.8�

�0.8�

�1.0�

�ns�

�MSC8126� Quad� Digital� Signal� Processor� Data� Sheet,� Rev.� 15�

�Freescale� Semiconductor�

�23�

�相关PDF资料 |

PDF描述 |

|---|---|

| GMM43DRYH | CONN EDGECARD 86POS DIP .156 SLD |

| RCC15DRES | CONN EDGECARD 30POS .100 EYELET |

| GEC15DREH | CONN EDGECARD 30POS .100 EYELET |

| FMC13DRAN | CONN EDGECARD 26POS R/A .100 SLD |

| VE-25N-CW-F2 | CONVERTER MOD DC/DC 18.5V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MSC8126VT8000 | 功能描述:IC DSP QUAD 16B 500MHZ 431FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| MSC81325M | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS AVIONICS APPLICATIONS |

| MSC81350M | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS AVIONICS APPLICATIONS |

| MSC81400M | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS AVIONICS APPLICATIONS |

| MSC81402 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS GENERAL PURPOSE AMPLIFIERS APPLICATIONS |

发布紧急采购,3分钟左右您将得到回复。